7가지 필수 표면 실장 패키지 유형이 현대 전자 설계의 중요한 구성 요소로 등장했으며 각각 고유한 장점과 응용 분야를 제공합니다. 여기에는 SOT(Small Outline Transistor) 패키지, QFP(Quad Flat Package) 변형, DFN(Dual Flat No-Lead) 패키지, BGA(Ball Grid Array) 패키지, LGA(Land Grid Array) 패키지, SOIC(Small Outline Integrated Circuit)가 포함됩니다. ) 패키지 및 CSP(Chip Scale Package) 옵션. 각 유형은 공간이 제한된 설계, 고전력 장치 및 고밀도 애플리케이션과 같은 특정 애플리케이션에 적합합니다. 각 패키지 유형의 특성을 이해함으로써 설계자는 향상된 성능과 신뢰성을 위해 전자 설계를 최적화할 수 있습니다. 이러한 패키지 유형을 더 자세히 살펴보면 해당 기능과 제한 사항에 대한 더 미묘한 통찰력을 얻을 수 있습니다.

주요 시사점

- SOT 패키지는 콤팩트한 두께와 다양성을 제공하여 전력 트랜지스터, 조정기, 증폭기와 같은 다양한 구성 요소를 지원합니다.

- QFP 변형은 다양한 리드 수, 피치 크기 및 치수를 제공하므로 높은 핀 밀도 애플리케이션에 적합합니다.

- DFN 패키지는 컴팩트한 크기와 열 관리 기능이 뛰어나 공간이 제한된 고전력 애플리케이션에 이상적입니다.

- BGA 및 LGA 패키지는 작은 설치 공간과 향상된 열 및 전기 성능을 특징으로 하여 고밀도 및 고속 신호 애플리케이션에 적합합니다.

- WLCSP 및 FOWLP와 같은 CSP 옵션은 고집적도, 최소한의 공간 요구 사항 및 향상된 I/O 밀도를 제공하므로 소형 전자 설계에 널리 사용됩니다.

SOT(소형 아웃라인 트랜지스터) 패키지

SOT(Small Outline Transistor) 패키지가 다른 표면 실장 기술과 구별되는 점은 다양한 핀 수, 리드 크기 및 피치를 모두 1.8mm의 컴팩트한 최대 두께 내에서 제공하는 다용성입니다. 이러한 다양성으로 인해 SOT 패키지는 다양한 애플리케이션에 널리 사용됩니다.

일반적인 SOT 패키지 유형에는 SOT-23, SOT-89, SOT-223, SOT-323및 SOT-363은 각각 특정 구성 요소 요구 사항을 충족합니다. 예를 들어 SOT-23은 저전력 트랜지스터에 자주 사용되는 반면 SOT-89는 전압 트랜지스터에 일반적으로 사용됩니다. 규제기관및 MOSFET의 경우 SOT-223입니다. SOT 패키지는 전력 트랜지스터, 레귤레이터, 다이오드, 증폭기, 그리고 광절연체.

특정 전력 요구 사항과 PCB 레이아웃 제약 조건을 충족하는 구성 요소를 선택하려면 SOT 패키지의 특성을 이해하는 것이 필수적입니다. 컴팩트한 크기와 적응성을 갖춘 SOT 패키지는 전력 및 성능을 위해 설계를 최적화하려는 설계자에게 이상적인 선택입니다.

QFP(쿼드 플랫 패키지) 변형

LQFP(로우 프로파일 쿼드 플랫 패키지) 및 TQFP(Thin Quad Flat 패키지)를 포함한 QFP(쿼드 플랫 패키지) 변형은 다양한 설계 요구 사항을 충족하기 위해 개발되었으며 다양한 제품을 제공합니다. 리드 수, 피치 크기및 효율적인 사용을 가능하게 하는 차원 회로 레이아웃 그리고 공간 활용. 이러한 변형은 설계자에게 특정 애플리케이션에 가장 적합한 패키지를 선택할 수 있는 유연성을 제공합니다.

- LQFP 패키지는 표준 QFP에 비해 높이가 낮아서 공간 효율성 컴팩트한 디자인을 가능하게 합니다.

- TQFP 패키지는 높이 제약이 중요한 애플리케이션을 위해 더 얇은 프로파일을 제공하여 슬림형 장치와의 호환성을 보장합니다.

- QFP 패키지는 다양한 회로 레이아웃 요구 사항을 수용하기 위해 다양한 리드 수, 피치 크기 및 치수로 제공됩니다.

QFP 패키지는 핀 밀도와 공간 제약 사이의 균형이 필요한 애플리케이션에 특히 적합합니다. 그들은 제공한다 높은 핀 수, 높은 수준의 통합이 요구되는 설계에 매력적인 옵션이 됩니다. 다양한 QFP 변형을 제공함으로써 설계자는 특정 성능을 충족하도록 설계를 최적화할 수 있습니다. 힘, 공간 요구 사항.

DFN(듀얼 플랫 무연) 패키지

DFN(Dual Flat No-Lead) 패키지는 현대 전자 설계에서 인기 있는 선택으로 부상했으며 다음과 같은 독특한 조합을 제공합니다. 컴팩트한 사이즈, 뛰어난 열 관리, 그리고 향상된 전기적 성능.

이것들 표면 실장 장치 특히 컴팩트한 크기와 공간 제약이 있는 애플리케이션에 적합합니다. 로우 프로파일 보드 공간을 효율적으로 사용할 수 있습니다.

DFN 패키지에 리드가 없기 때문에 기생 효과가 최소화되어 향상된 성능을 제공합니다. 고주파 성능 기존 납 함유 패키지에 비해 신뢰성이 높습니다.

또한 DFN 패키지 하단의 노출 패드는 열 전도성, 더 나은 방열 및 열 관리 기능을 제공합니다. 따라서 효율적인 열 방출이 중요한 고전력 애플리케이션에 이상적입니다.

결과적으로 DFN 패키지로 패키징된 반도체 부품은 고신뢰성 및 고성능 시스템을 비롯한 광범위한 애플리케이션에서 점점 더 많이 사용되고 있습니다.

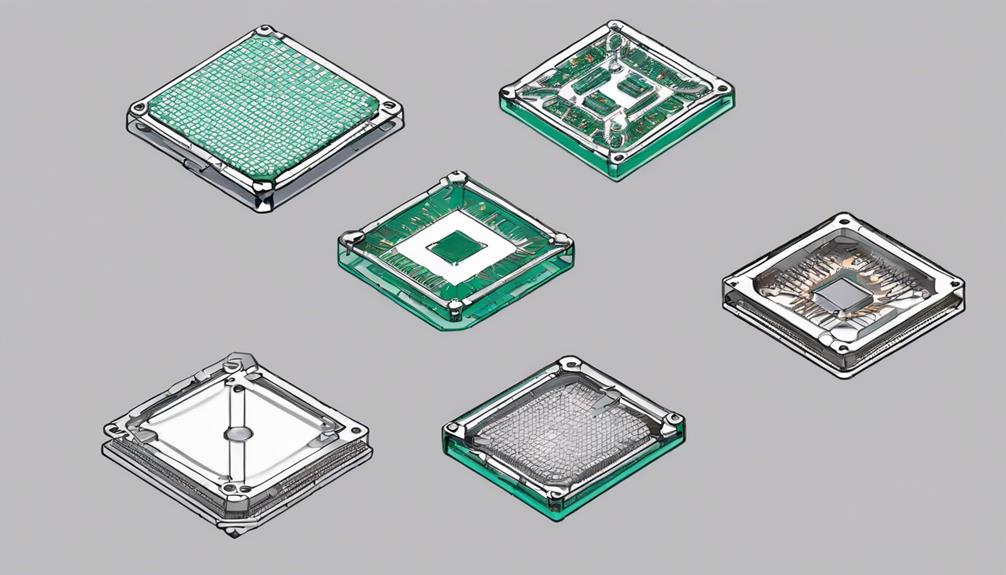

BGA(볼 그리드 어레이) 패키지

BGA(Ball Grid Array) 패키지는 고밀도 전자 설계를 위한 선호되는 선택으로 부상했으며, 보드 공간을 효율적으로 사용할 수 있는 컴팩트한 설치 공간과 견고한 연결의 고유한 조합을 제공합니다. 이는 공간 효율성이 중요한 IC 패키징에서 특히 중요합니다.

BGA 패키지에는 패키지 아래에 솔더 볼을 사용하여 연결된 접촉 패드가 있습니다. 1.27mm의 일반적인 볼 피치는 안정적인 납땜을 보장합니다.

BGA 패키지의 장점은 다음과 같습니다.

- 컴팩트한 설치 공간: BGA 패키지는 다른 패키지 유형에 비해 설치 공간이 작아 고밀도 애플리케이션에 이상적입니다.

- 견고한 연결: 솔더 볼은 안정적인 연결을 제공하여 보드 공간의 효율적인 사용을 보장합니다.

- 높은 핀 수: BGA 패키지는 많은 수의 핀을 수용할 수 있어 복잡한 전자 설계에 적합합니다.

BGA 패키지로 작업할 때 성공적인 납땜을 보장하려면 적절한 PCB 조립 기술을 사용하는 것이 필수적입니다. 이는 작은 외형 패키지에 정밀한 조립이 필요한 표면 실장 기술에 매우 중요합니다.

LGA(랜드 그리드 어레이) 패키지

LGA(Land Grid Array) 패키지는 고성능 애플리케이션을 위한 선호되는 선택으로 부상했습니다. 토지의 배열 믿을 수 있는 제공하기 위하여 바닥 표면에 전기 연결 솔더볼을 통해

리드가 있는 기존 패키지와 달리 LGA 패키지에는 다양한 랜드가 포함되어 있습니다. 향상된 열 및 전기 성능. 이 설계를 통해 LGA 패키지는 핀 수가 많고 핀 수가 많은 고성능 애플리케이션에서 탁월한 성능을 발휘할 수 있습니다. 컴팩트한 설치 공간 필수적입니다.

그만큼 단서가 없음 또한 더 나은 열 방출을 촉진하므로 LGA 패키지는 고속 신호와 낮은 인덕턴스가 중요한 애플리케이션에 이상적입니다. LGA 패키지의 컴팩트한 설치 공간 덕분에 보드 공간을 효율적으로 사용할 수 있으므로 공간이 제한된 애플리케이션에 적합합니다.

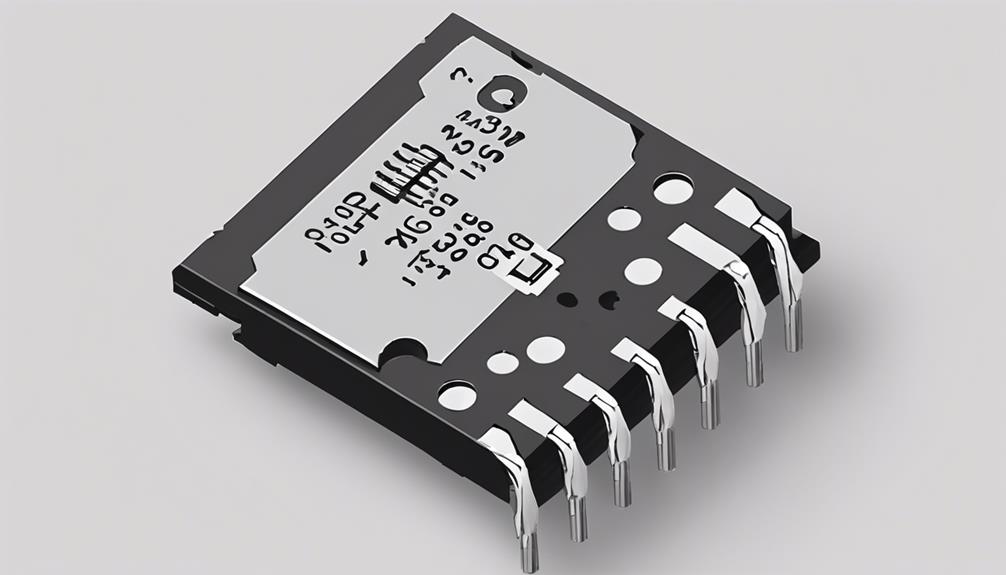

SOIC(소형 아웃라인 집적 회로) 패키지

SOIC(Small Outline Integrated Circuit) 패키지 영역에서는 패키지 크기, 핀 수 옵션 및 세 가지 주요 측면을 검토해야 합니다. 내열성.

이러한 요소는 성능과 신뢰성에 영향을 미칩니다. SOIC 패키지, 이는 다양한 IC 애플리케이션에 널리 사용됩니다.

패키지 크기

작은 크기와 다용도성을 갖춘 SOIC(Small Outline Integrated Circuit) 패키지는 현대 전자 제품의 필수 요소가 되었으며 SOIC-8을 비롯한 다양한 크기를 제공합니다. SOIC-14및 SOIC-16은 각각 해당 핀 수로 식별됩니다. SOIC 패키지의 표준화된 패키지 크기는 PCB 레이아웃 및 설계와의 원활한 통합을 보장합니다.

SOIC 패키지의 리드 피치는 1.27mm로 다양한 SMD 부품과의 호환성이 용이합니다. SOIC 패키지의 걸윙 리드를 사용하면 안전한 표면 실장을 가능하게 하여 안정적인 연결과 간편한 조립을 보장합니다. SOIC 패키지의 로우 프로파일 설계는 공간이 제한된 애플리케이션에 이상적이므로 IC, 증폭기, 전압 조정기 및 기타 집적 회로에 널리 사용됩니다.

SOIC 패키지의 패키지 크기는 특정 애플리케이션에 대한 적합성을 결정하는 데 중요합니다. 패키지 크기, 패드 크기 및 리드 피치를 이해함으로써 설계자와 엔지니어는 PCB 설계를 최적화하여 효율적인 공간 사용과 안정적인 성능을 보장할 수 있습니다.

결과적으로 SOIC 패키지는 다양한 장치와 시스템에 전력을 공급하는 현대 전자 장치의 초석이 되었습니다.

핀 수 옵션

SOIC 패키지는 다양한 기능을 제공합니다. 핀 수 다양한 수준의 복잡성을 충족하는 옵션 집적 회로 디자인을 통해 디자이너는 기능성과 기능성 사이의 균형을 찾을 수 있습니다. 공간적 제약. 핀 수 선택은 집적 회로의 복잡성과 설계의 공간적 제한에 따라 달라집니다.

일반적인 핀 수 옵션 SOIC 패키지 8, 14, 16, 20 및 28핀이 포함되며 핀 수는 일반적으로 단순화하기 위해 4의 배수입니다. PCB 레이아웃 그리고 라우팅.

핀 수와 관련된 SOIC 패키지의 유연성을 통해 설계자는 특정 애플리케이션에 맞게 설계를 최적화할 수 있습니다. 선택할 수 있는 핀 수가 다양하므로 설계자는 집적 회로에 가장 적합한 패키지를 선택할 수 있으므로 PCB 공간을 효율적으로 사용할 수 있습니다.

핀 밀도와 납땜 용이성 사이의 균형 표면 실장 기술 SOIC 패키지의 중요한 장점입니다. 다양한 핀 수 옵션을 제공함으로써 SOIC 패키지는 설계자가 특정 성능 요구 사항을 충족하는 효율적이고 효과적인 설계를 생성할 수 있는 자유를 제공합니다. 공간 제약.

내열성

열 저항, 중추적인 매개변수 표면 실장 기술는 SOIC(Small Outline Integrated Circuit) 패키지의 신뢰성과 성능을 결정하는 데 중요한 역할을 합니다. SOIC 패키지에서는 내열성 일반적으로 약 30~70°C/W로 열을 효율적으로 발산하는 능력을 나타냅니다.

열 저항 값이 낮을수록 더 좋음을 의미합니다. 열 성능, 이는 매우 중요합니다. 고전력 애플리케이션. 최적의 성능을 보장하려면 표면 실장 패키지를 설계할 때 열 저항을 고려하는 것이 중요합니다.

주요 고려 사항은 다음과 같습니다.

- 열 저항은 접합부-주위 열 저항에 영향을 미치며 SOIC 부품의 전체 작동 온도에 영향을 미칩니다.

- 적절한 열 관리 기술 좋다 방열판 또는 열 비아는 SOIC 패키지의 열 성능을 향상시킬 수 있습니다.

- 열 저항 값을 이해하면 효과적인 설계에 도움이 됩니다. 방열 솔루션 SOIC 부품용.

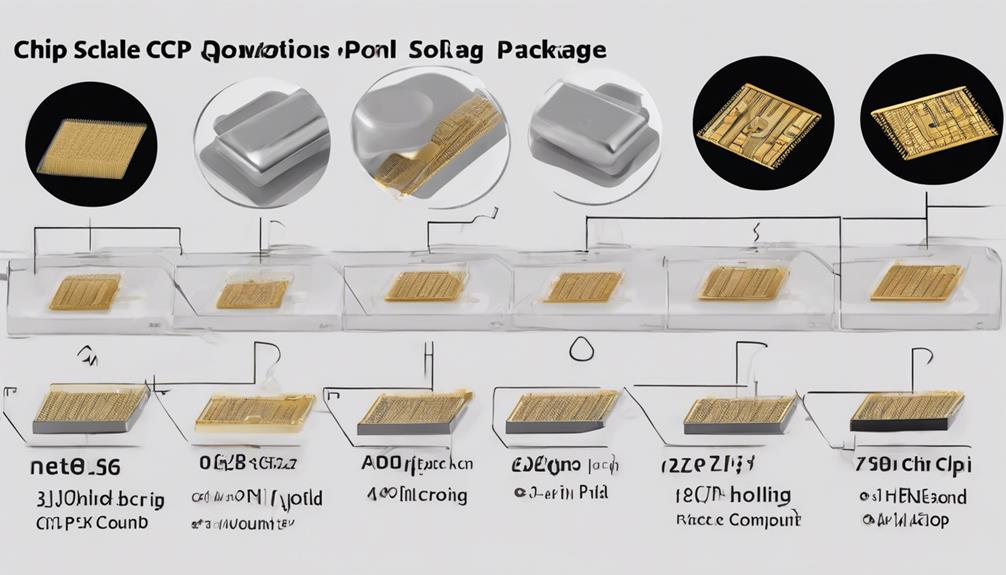

칩 스케일 패키지(CSP) 옵션

CSP(칩 스케일 패키지)는 매우 작은 설치 공간 내에 복잡한 기능을 통합할 수 있는 뛰어난 능력으로 인해 소형 전자 설계에서 선호되는 경우가 많습니다.

각 측면의 크기가 1mm 미만인 CSP는 최소한의 설치 공간으로 높은 통합성을 제공하므로 공간이 제한된 애플리케이션에 이상적입니다. 추가 패키징 구성 요소를 제거하면 전기 성능이 향상되어 효율적인 데이터 전송이 가능하고 전력 소비가 줄어듭니다.

WLCSP(웨이퍼 레벨 칩 스케일 패키지) 및 FOWLP(팬아웃 웨이퍼 레벨 패키지)와 같은 변형은 다음과 같은 고급 기능을 제공합니다. I/O 밀도 증가 그리고 개선됨 열 관리. CSP 옵션에는 BGA와 유사한 디자인이 포함됩니다. 솔더볼 또는 팬아웃 구성으로 기능과 신뢰성이 향상됩니다.

이러한 컴팩트한 패키지는 모바일 장치에 널리 사용되며, 웨어러블, 그리고 IoT 제품, 컴팩트한 크기와 효율적인 성능이 필수적인 곳입니다. CSP를 활용함으로써 디자이너는 혁신적이고 고성능 장치 현대 전자 제품의 요구 사항을 충족합니다.

자주 묻는 질문

다양한 유형의 SMD 패키지는 무엇입니까?

전자 산업이 지속적으로 소형화되면서 SMD(Surface Mount Device) 패키지의 중요성이 부각되고 있습니다.

'다양한 유형의 SMD 패키지는 무엇입니까?'라는 질문에 대한 응답으로 수많은 옵션이 나타납니다. QFP, BGA, SOIC 및 PLCC는 널리 사용되는 변형인 반면 LQFP, TQFP 및 TSOP는 특정 IC 구성 및 핀 간격을 지원합니다.

또한 SOT-23, SOT-89 및 SOT-223과 같은 SOT 패키지는 일반적으로 개별 부품에 사용되어 설계 유연성과 효율성을 제공합니다.

다양한 유형의 표면 실장 리드는 무엇입니까?

표면 실장 리드는 다양한 구성으로 제공되며 각각 고유한 특성을 가지고 있습니다.

SOIC 패키지에서 흔히 볼 수 있는 걸윙 리드는 납땜 중에 기계적 안정성을 제공합니다.

QFP 패키지에서 흔히 볼 수 있는 J-리드 패키지는 향상된 열 및 전기 성능을 제공합니다.

일반적으로 PLCC 패키지에 있는 플랫 리드를 사용하면 공간이 제한된 애플리케이션을 위한 로우 프로파일 설계가 가능합니다.

이러한 리드 구성은 납땜 프로세스, 열 관리 및 전반적인 구성 요소 신뢰성에 상당한 영향을 미칩니다. 표면 실장 패키지.

SOT와 SOIC 패키지의 차이점은 무엇입니까?

SOT의 주요 차이점(소형 아웃라인 트랜지스터) 및 SOIC(소형 외형 집적 회로) 패키지는 디자인, 응용 프로그램 및 특성에 따라 다릅니다.

SOT 패키지는 더 작습니다. 갈매기 날개 리드, 일반적으로 트랜지스터 및 다이오드와 같은 개별 구성 요소에 사용됩니다.

이와 대조적으로 SOIC 패키지는 집적 회로에 일반적으로 사용되는 J-리드를 사용하여 더 큽니다.

표면 실장 패키지란 무엇입니까?

현대 전자 분야에서는 중요한 질문이 대두됩니다. 표면 실장 패키지?

그 답은 혁신과 효율성의 교차점에 있습니다. 표면 실장 패키지는 표면에 직접 배치하도록 설계되었습니다. 프린트 배선판, 구멍을 뚫을 필요가 없습니다.

이 혁신적인 접근 방식은 공간 절약형 설계, 향상된 전기 성능 및 간소화된 조립 프로세스를 가능하게 합니다. 활용하여 표면 실장 기술, 제조업체는 달성할 수 있습니다 더 높은 부품 밀도, 더 빠른 생산 속도, 그리고 비교할 수 없는 신뢰성을 제공합니다.