Thiết kế để có thể kiểm tra là một khía cạnh thiết yếu của thiết kế bảng mạch in (PCB), đảm bảo việc kiểm tra hiệu quả, sớm phát hiện lỗivà giảm thời gian và nguồn lực để xác định lỗi. Hiệu quả thiết kế để kiểm tra liên quan đến việc thực hiện điểm kiểm tra một cách chiến lược, duy trì thông thoáng và khả năng tiếp cận, đồng thời tối ưu hóa định tuyến tín hiệu. Nó cũng bao gồm việc sử dụng các vectơ thử nghiệm một cách hiệu quả, thiết kế để có thể sản xuất được và nâng cao phạm vi kiểm tra và chất lượng. Bằng cách tuân theo các phương pháp thực hành thiết yếu nhất, nhà thiết kế có thể đảm bảo phạm vi kiểm tra kỹ lưỡng, giảm độ phức tạp của kiểm tra và hợp lý hóa quá trình sản xuất. Khi tầm quan trọng của khả năng kiểm tra tiếp tục tăng lên, việc hiểu các nguyên tắc này ngày càng trở nên quan trọng để thiết kế và sản xuất PCB thành công.

Bài học chính

- Đảm bảo phạm vi kiểm tra kỹ lưỡng bằng cách kết hợp các điểm CNTT trên mọi mạng thiết kế và bố trí các điểm kiểm tra một cách chiến lược về khả năng tiếp cận.

- Triển khai các chiến lược bố trí PCB duy trì khoảng cách từ các thành phần, khoảng cách cạnh và vị trí đặt điểm thăm dò chiến lược để giảm độ phức tạp của quá trình thử nghiệm.

- Thiết kế để có thể sản xuất được bằng cách đặt các điểm ICT trên mọi lưới thiết kế, đảm bảo các điểm kiểm tra có thể tiếp cận được với khoảng cách dễ dàng và tuân thủ các hướng dẫn DFT.

- Sử dụng các vectơ kiểm tra hiệu quả được tạo thông qua các phương pháp như phương pháp giả ngẫu nhiên, toàn diện, thông minh và dựa trên ràng buộc để tối đa hóa phạm vi bao phủ lỗi.

- Nâng cao phạm vi và chất lượng kiểm tra bằng cách kết hợp các điểm CNTT, tiến hành kiểm tra rộng rãi và triển khai kiểm tra đơn vị để xác định kịp thời các lỗi sản xuất và lỗi linh kiện.

Thiết kế cho các nguyên tắc cơ bản về khả năng kiểm tra

Thiết kế để kiểm thử (DFT) là một khái niệm thiết yếu trong phát triển phần mềm và phần cứng, nhấn mạnh đến việc tạo ra các thành phần thúc đẩy thử nghiệm dễ dàng, từ đó đảm bảo chất lượng và độ tin cậy tốt hơn của sản phẩm cuối cùng.

Bằng cách kết hợp các nguyên tắc DFT, các nhà phát triển có thể tạo ra các thành phần phần mềm có lợi cho các loại thử nghiệm khác nhau, bao gồm thử nghiệm đơn vị, tích hợp, chức năng, tải và hiệu suất. Cách tiếp cận toàn diện này để thử nghiệm cho phép phát hiện lỗi và sai sót sớm trong chu kỳ phát triển, làm giảm khả năng xảy ra các vấn đề ở hạ nguồn.

DFT hiệu quả xem xét toàn bộ phổ thử nghiệm, đảm bảo rằng các thành phần được thiết kế có tính đến khả năng thử nghiệm. Cách tiếp cận này tạo điều kiện thuận lợi cách ly lỗi nhanh, giảm thời gian và nguồn lực cần xác định và khắc phục lỗi sản xuất và lỗi linh kiện.

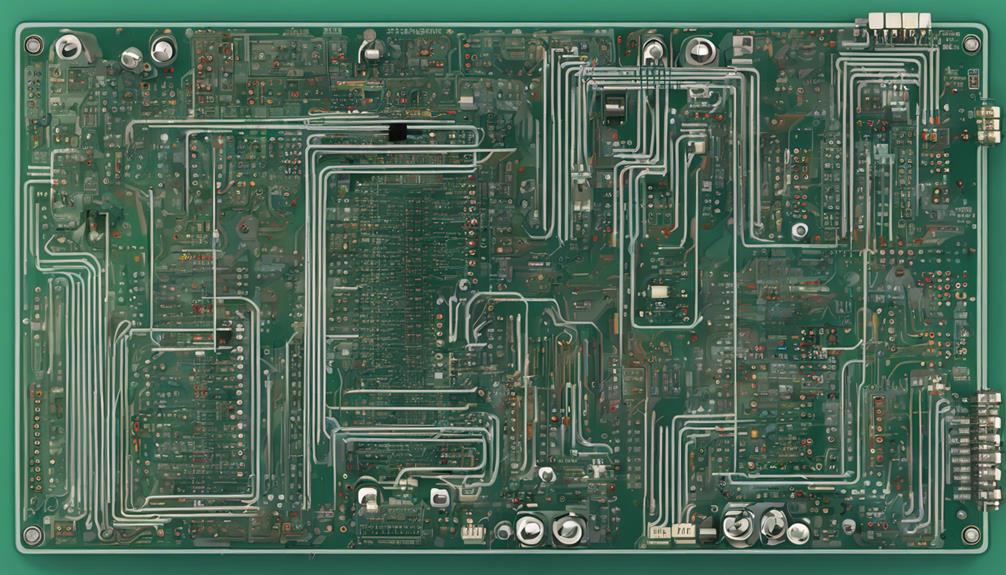

Bố cục PCB để có khả năng kiểm tra tối đa

Để có thể kiểm tra kỹ lưỡng, bố cục bảng mạch in (PCB) phải được thiết kế với các điểm kiểm tra có chủ ý và các tính năng trợ năng tạo điều kiện thuận lợi cho việc kiểm tra và chẩn đoán lỗi hiệu quả. Bố cục PCB được thiết kế tốt có thể giảm đáng kể độ phức tạp và chi phí thử nghiệm.

Để đạt được khả năng kiểm tra tối đa, cần tuân thủ các nguyên tắc sau:

- Phạm vi kiểm tra kỹ lưỡng: Thiết kế bố cục PCB với các điểm CNTT trên mỗi mạng để đảm bảo phạm vi kiểm tra kỹ lưỡng.

- Giải phóng mặt bằng từ các thành phần: Duy trì khoảng cách tối thiểu 50 mil giữa các điểm kiểm tra và các thành phần và miếng đệm.

- Giải phóng mặt bằng: Duy trì khoảng cách 100 mil giữa các điểm kiểm tra và cạnh của bảng để dễ tiếp cận.

- Vị trí điểm thăm dò: Đặt các điểm thăm dò một cách chiến lược để kiểm tra thủ công nhằm tạo điều kiện cho các kỹ thuật viên dễ dàng tiếp cận.

Triển khai các điểm kiểm tra một cách chiến lược

Các điểm kiểm tra được bố trí ở vị trí chiến lược là cần thiết để đảm bảo bao phủ toàn diện các kết nối quan trọng trên PCB, tạo điều kiện thuận lợi cho việc kiểm tra. kiểm tra hiệu quả và chẩn đoán lỗi.

Bằng cách kết hợp các điểm kiểm tra vào thiết kế PCB, các kỹ sư có thể đảm bảo rằng các bài kiểm tra đơn vị là chi tiết và có thể nhanh chóng xác định và cách ly các lỗi.

Để đạt được khả năng kiểm tra lý tưởng, các điểm kiểm tra phải được đặt ở vị trí chiến lược có tính đến khả năng tiếp cận, khoảng trống và yêu cầu toàn vẹn tín hiệu. Khoảng cách thích hợp giữa các điểm kiểm tra cũng rất quan trọng để ngăn ngừa đoản mạch và đảm bảo thủ tục kiểm tra đáng tin cậy.

Hơn nữa, các điểm kiểm tra được bố trí gần các bộ phận chính cho phép thực hiện hiệu quả cách ly lỗi và khắc phục sự cố trong quá trình thử nghiệm.

Việc bố trí các điểm kiểm tra một cách hiệu quả không chỉ đơn giản hóa quá trình kiểm tra mà còn giảm thiểu sự phức tạp của các thiết bị kiểm tra, giảm thiểu chi phí và thời gian kiểm tra.

Thiết kế có thể kiểm tra để sản xuất

Việc tối ưu hóa bố cục PCB cho khả năng sản xuất đòi hỏi một thiết kế có thể kiểm tra được, tích hợp các điểm CNTT trên mọi mạng thiết kế để đảm bảo phạm vi kiểm tra kỹ lưỡng và tạo điều kiện thuận lợi cho quy trình sản xuất hiệu quả. Cách tiếp cận này cho phép các nhà sản xuất theo hợp đồng (CM) tiến hành thử nghiệm CNTT, đảm bảo rằng cả hai mặt của PCB đều được thử nghiệm đồng thời.

Để đảm bảo khả năng kiểm tra hiệu quả, cần tuân thủ các nguyên tắc sau:

- Điểm kiểm tra có thể truy cập: Đảm bảo khoảng cách 50 mil với các bộ phận và miếng đệm để dễ dàng tiếp cận.

- Vị trí chiến lược: Định vị các điểm kiểm tra dựa trên hướng dẫn của DFT để giảm độ phức tạp của thiết bị cố định và các chi phí bổ sung tiềm ẩn.

- Kiểm tra thủ công dễ dàng: Đặt các điểm thăm dò để kỹ thuật viên có thể dễ dàng tiếp cận.

- Kiểm tra phối hợp: Cộng tác với CM để điều phối thử nghiệm CNTT để có quy trình sản xuất hiệu quả.

Sử dụng hiệu quả các vectơ thử nghiệm

Trong miền của thiết kế để kiểm tra, việc sử dụng hiệu quả các vectơ kiểm tra là rất quan trọng để đảm bảo kiểm tra kỹ lưỡng chức năng của mạch.

Để đạt được điều này, điều cần thiết là phải sử dụng các phương pháp tạo vectơ hiệu quả để có thể tạo ra một tập hợp vectơ thử nghiệm đa dạng, từ đó tối ưu hóa Kiểm tra vùng phủ sóng.

Phương pháp tạo vectơ

Thông thường, hiệu quả của thiết kế cho khả năng kiểm tra phụ thuộc rất nhiều vào việc tạo ra các vectơ kiểm tra hiệu quả, điều này rất cần thiết để xác minh hành vi của thiết kế đang được kiểm tra (DUT).

Trong thử nghiệm đơn vị, vectơ thử nghiệm là các mẫu đầu vào được sử dụng để xác minh hoạt động của DUT và việc tạo ra chúng hiệu quả là rất quan trọng để bao phủ toàn diện chức năng DUT.

Để đảm bảo thử nghiệm hiệu quả, nhiều thuật toán khác nhau có thể được sử dụng để tạo vectơ thử nghiệm. Bao gồm các:

- Tạo vectơ thử nghiệm giả ngẫu nhiên, cân bằng tính ngẫu nhiên và độ lặp lại để thử nghiệm hiệu quả.

- Tạo vectơ thử nghiệm toàn diện, bao gồm việc tạo ra tất cả các mẫu đầu vào có thể.

- Tạo vector thông minh, giúp tối ưu hóa phạm vi kiểm tra đồng thời giảm thiểu thời gian và tài nguyên kiểm tra.

- Tạo vectơ thử nghiệm dựa trên ràng buộc, tạo ra các vectơ kiểm tra dựa trên các ràng buộc cụ thể và nguyên tắc kiểm tra.

Tối ưu hóa phạm vi kiểm tra

Tối ưu hóa phạm vi kiểm tra

Lựa chọn chiến lược các điểm kiểm tra là điều cần thiết để tối đa hóa phạm vi lỗi trong kiểm tra PCB, vì nó cho phép sử dụng hiệu quả các vectơ kiểm tra để nhắm mục tiêu vào các khu vực cụ thể của thiết kế đang được kiểm tra. Cách tiếp cận này đảm bảo rằng các khuyết tật tiềm ẩn được xác định và giải quyết, giảm nguy cơ PCB bị lỗi. Việc phân bổ các vectơ kiểm tra hợp lý có thể giảm đáng kể thời gian kiểm tra trong khi vẫn đảm bảo phạm vi bao phủ toàn diện.

| Kỹ thuật tối ưu hóa | Những lợi ích |

|---|---|

| Kiểm tra quét ranh giới | Nâng cao hiệu quả vectơ thử nghiệm bằng cách truy cập các nút nội bộ |

| Tái sử dụng vectơ thử nghiệm | Giảm thời gian thử nghiệm và cải thiện phân bổ nguồn lực |

| Kiểm tra định hướng khiếm khuyết | Kiểm tra mục tiêu các khu vực có xác suất lỗi cao |

| Thử nghiệm dựa trên ATPG | Bảo hiểm lỗi hiệu quả với việc tạo mẫu thử nghiệm tự động |

| Thử nghiệm lai | Kết hợp các kỹ thuật khác nhau để bao phủ toàn diện |

Đơn giản hóa thiết kế mạch phức tạp

Chia các mạch phức tạp thành các thành phần nhỏ hơn, dễ quản lý hơn là một bước thiết yếu trong việc đơn giản hóa thiết kế mạch phức tạp. Điều này cho phép các nhà thiết kế xử lý từng mô-đun riêng lẻ, nâng cao khả năng kiểm tra tổng thể. Cách tiếp cận này cho phép các nhà thiết kế tập trung vào các mô-đun cụ thể, giảm độ phức tạp của thiết kế tổng thể.

Để đạt được điều này, các nhà thiết kế có thể sử dụng một số chiến lược:

- Thiết kế mô-đun: Việc chia nhỏ các mạch phức tạp thành các mô-đun có thể tái sử dụng sẽ giúp việc kiểm tra và bảo trì dễ dàng hơn.

- Giảm sự phụ thuộc: Giảm thiểu sự phụ thuộc giữa các thành phần giúp đơn giản hóa thiết kế và cải thiện khả năng cách ly lỗi.

- Xóa tài liệu: Cung cấp tài liệu ngắn gọn và rõ ràng về các thiết kế mạch phức tạp sẽ tạo điều kiện thuận lợi cho việc hiểu và thử nghiệm chức năng của thiết kế.

- Mẫu thiết kế: Việc triển khai các mẫu thiết kế, chẳng hạn như mẫu Observer, có thể đơn giản hóa các tương tác mạch phức tạp và cải thiện khả năng kiểm tra.

Định tuyến tín hiệu hiệu quả để kiểm tra

Khi thiết kế để có thể kiểm tra, hiệu quả định tuyến tín hiệu là cần thiết để đảm bảo phép đo chính xácvà chiến lược định tuyến tín hiệu được hoạch định tốt có thể giảm đáng kể lỗi và nâng cao hiệu quả thử nghiệm.

Để đạt được điều này, điều quan trọng là phải giảm thiểu độ dài tín hiệu để đảm bảo các phép đo chính xác. Hơn nữa, các cặp tín hiệu vi sai nên được định tuyến cùng nhau để duy trì tính toàn vẹn tín hiệu trong quá trình thử nghiệm. Điều này ngăn cản suy giảm tín hiệu và đảm bảo kết quả kiểm tra đáng tin cậy.

Ngoài ra, điều quan trọng là tránh định tuyến tín hiệu gần các bộ phận gây nhiễu để tránh nhiễu trong quá trình thử nghiệm. Dấu vết trở kháng được kiểm soát nên được sử dụng để duy trì tính toàn vẹn và độ chính xác của tín hiệu trong quá trình thử nghiệm. Điều này đảm bảo rằng các tín hiệu kiểm tra không bị méo, mang lại kết quả kiểm tra đáng tin cậy.

Việc triển khai các điểm kiểm tra tại các vị trí chiến lược cũng rất quan trọng để dễ dàng tiếp cận và thực hiện quy trình kiểm tra hiệu quả. Bằng cách kết hợp những điều này cân nhắc thiết kế, các nhà thiết kế có thể đảm bảo rằng chiến lược định tuyến tín hiệu của họ được tối ưu hóa để có thể kiểm tra, mang lại kết quả kiểm tra hiệu quả và chính xác.

Định tuyến tín hiệu hiệu quả là một khía cạnh quan trọng của thiết kế để có khả năng kiểm tra và bằng cách làm theo các phương pháp hay nhất này, các nhà thiết kế có thể đảm bảo việc kiểm tra hiệu quả và đáng tin cậy.

Thiết kế để kiểm tra trong mạch

Khi thiết kế bảng mạch in (PCB) để kiểm tra trong mạch (ICT), phải xem xét cẩn thận việc sắp xếp các bộ phận, xác định các thành phần. điểm kiểm tra, Và định tuyến tín hiệu để đảm bảo việc kiểm tra hiệu quả và hiệu quả. Bằng cách tối ưu hóa các yếu tố này, các nhà thiết kế có thể tạo điều kiện thuận lợi cho việc phủ sóng CNTT và cách ly lỗi nhanh chóng, cuối cùng là giảm chi phí sản xuất và cải thiện chất lượng sản phẩm.

Trong các phần sau, chúng ta sẽ xem xét các những điểm chính về vị trí thành phần có thể truy cập, xác định điểm kiểm tra và cân nhắc định tuyến tín hiệu để tạo điều kiện cho CNTT thành công.

Vị trí thành phần có thể truy cập

Vị trí thành phần có thể tiếp cận phù hợp là điều cần thiết trong việc thiết kế thử nghiệm trong mạch, vì nó cho phép bố trí điểm kiểm tra hiệu quả và đảm bảo phạm vi kiểm tra toàn diện. Điều này rất quan trọng đối với thử nghiệm đơn vị vì nó đảm bảo rằng mã thiết kế có thể được kiểm tra toàn diện.

Trong kiểm tra CNTT, các điểm kiểm tra được đặt ở vị trí chiến lược để tạo điều kiện cho các thiết bị và kỹ thuật viên kiểm tra dễ dàng tiếp cận, giảm bớt sự phức tạp trong kiểm tra.

Để đạt được vị trí thành phần lý tưởng, nhà thiết kế nên xem xét các nguyên tắc sau:

- Yêu cầu giải phóng mặt bằng: Đảm bảo khoảng hở 50 mil đối với các linh kiện và 100 mil đối với mép bo mạch.

- Vị trí điểm kiểm tra: Xác định vị trí chiến lược các điểm kiểm tra trên bố cục PCB, xem xét các yêu cầu về khoảng trống để kiểm tra hiệu quả.

- Khả năng tiếp cận thành phần: Đảm bảo các thành phần có thể truy cập được cho mục đích thử nghiệm, giảm độ phức tạp của thử nghiệm.

- Phạm vi kiểm tra hiệu quả: Đảm bảo phạm vi kiểm tra kỹ lưỡng bằng cách đặt điểm kiểm tra theo cách cho phép kiểm tra toàn diện.

Xác định điểm kiểm tra

Để theo đuổi việc kiểm tra hiệu quả trong mạch, xác định điểm kiểm tra đóng một vai trò quan trọng trong thiết kế PCB, vì nó cho phép bố trí chiến lược các điểm dành riêng cho CNTT trên bảng. Sự sắp xếp có chủ ý này của Điểm kiểm tra CNTT đảm bảo rằng chúng có thể tiếp cận dễ dàng, có khoảng cách vừa đủ với các bộ phận và cạnh bo mạch, cho phép thử nghiệm hiệu quả Trong quá trình sản xuất.

Khoảng cách thích hợp giữa các điểm kiểm tra cũng rất cần thiết vì nó đảm bảo việc kiểm tra chính xác và hiệu quả. Những điểm kiểm tra này tạo điều kiện thuận lợi cho việc kết nối thiết bị CNTT, cho phép các quy trình thử nghiệm tự động.

Ngoài ra, các điểm kiểm tra được đặt đúng vị trí và được dán nhãn cho phép nhanh chóng cách ly lỗi Và gỡ lỗi trong CNTT, tạo điều kiện thuận lợi cho việc xác định và khắc phục sự cố. Xác định điểm kiểm tra hiệu quả trong thiết kế PCB là rất quan trọng để kiểm tra hiệu quả trong mạch, hợp lý hóa quy trình kiểm tra và giảm thời gian sản xuất.

Cân nhắc định tuyến tín hiệu

Việc cân nhắc định tuyến tín hiệu đóng một vai trò quan trọng trong việc thiết kế thử nghiệm trong mạch vì chúng ảnh hưởng trực tiếp đến độ chính xác và độ tin cậy của kết quả thử nghiệm. Định tuyến tín hiệu thích hợp là điều cần thiết để đảm bảo kiểm tra PCB hiệu quả. Trong CNTT, độ dài đường dẫn tín hiệu phải được giảm thiểu và nên sử dụng định tuyến trở kháng có kiểm soát để ngăn chặn sự suy giảm tín hiệu.

Để đạt được thử nghiệm đáng tin cậy, cần cân nhắc việc định tuyến tín hiệu sau:

- Giảm thiểu sự chéo: Tránh các tín hiệu chồng lên nhau để tránh nhiễu điện từ và suy giảm tín hiệu.

- Tránh những khúc cua gấp: Sử dụng các tuyến đường cong, trơn tru để tránh phản xạ tín hiệu và bức xạ.

- Giới hạn vias: Giảm thiểu việc sử dụng vias để tránh mất và suy giảm tín hiệu.

- Vị trí điểm kiểm tra chiến lược: Đặt các điểm kiểm tra một cách chiến lược để tạo điều kiện cho các đầu dò kiểm tra tiếp cận dễ dàng, đảm bảo việc kiểm tra hiệu quả và đáng tin cậy.

Tăng cường phạm vi và chất lượng thử nghiệm

Các chiến lược kiểm tra hiệu quả, chẳng hạn như kết hợp các điểm CNTT trên mỗi mạng thiết kế, rất quan trọng để đảm bảo phạm vi kiểm tra kỹ lưỡng và chất lượng trong sản xuất PCB. Cách tiếp cận này cho phép Thử nghiệm rộng rãi, giảm khả năng xảy ra lỗi sản xuất và lỗi linh kiện mà không bị phát hiện.

Bằng cách bao gồm các điểm kiểm tra có khoảng cách thích hợp với các bộ phận và cạnh của bo mạch, kỹ thuật viên có thể tiến hành một cách hiệu quả. kiểm tra đơn vị và xác định vấn đề kịp thời. Ngoài ra, CNTT có thể được tiến hành đồng thời ở cả hai bên với sự phối hợp từ nhà sản xuất theo hợp đồng, hợp lý hóa quy trình thử nghiệm.

Hơn nữa, việc có các điểm thăm dò dễ tiếp cận để kiểm tra thủ công giúp đơn giản hóa các quy trình kiểm tra, giảm nguy cơ lỗi của con người. Phạm vi kiểm tra quan trọng và đảm bảo chất lượng là rất cần thiết trong việc xác định kịp thời các lỗi sản xuất và hư hỏng linh kiện, đảm bảo rằng chỉ PCB chất lượng cao được tung ra thị trường.

Tối ưu hóa thiết kế PCB để thử nghiệm

Khi tối ưu hóa thiết kế PCB cho thử nghiệm, điều quan trọng là phải tính đến vị trí của điểm kiểm tra, đảm bảo rằng chúng có thể dễ dàng tiếp cận để thử nghiệm hiệu quả.

Vị trí đặt điểm kiểm tra thích hợp tạo điều kiện thuận lợi cho việc kiểm tra kỹ lưỡng Kiểm tra vùng phủ sóng, giảm thời gian thử nghiệm và tăng chất lượng thử nghiệm.

Thiết kế cho khả năng tiếp cận

Bố cục PCB được thiết kế tốt kết hợp các điểm kiểm tra có thể truy cập sẽ hỗ trợ các quy trình kiểm tra hiệu quả, giảm thời gian và chi phí liên quan đến việc xác định và khắc phục lỗi. Thiết kế cho khả năng tiếp cận là một khía cạnh quan trọng của việc tối ưu hóa thiết kế PCB cho thử nghiệm, vì nó tạo điều kiện thuận lợi cho quá trình thử nghiệm và đảm bảo phạm vi bao phủ lỗi triệt để.

Để đạt được khả năng tiếp cận lý tưởng, các nhà thiết kế nên cân nhắc các yếu tố chính sau:

- Khoảng trống từ các thành phần và cạnh bo mạch: Đảm bảo các điểm kiểm tra có đủ khoảng trống để cho phép các đầu dò kiểm tra dễ dàng tiếp cận.

- Điểm ICT trên mỗi lưới thiết kế:Kết hợp các điểm ICT trên mỗi lưới thiết kế để có thể kiểm tra toàn diện trong quá trình sản xuất.

- Hợp tác với các nhà sản xuất hợp đồng: Làm việc với các nhà sản xuất theo hợp đồng để xác định các phương pháp thử nghiệm hiệu quả nhất và sửa đổi thiết bị cố định để nâng cao phạm vi bảo hiểm lỗi.

- Kiểm tra CNTT để có phản hồi ngay lập tức: Sử dụng thử nghiệm CNTT để nhận phản hồi ngay lập tức về lỗi sản xuất, lỗi linh kiện và chức năng tổng thể của PCB, cho phép điều chỉnh nhanh chóng.

Vị trí điểm kiểm tra

Việc đặt các điểm kiểm tra trên PCB một cách chiến lược là điều cần thiết để có phạm vi bao phủ tối đa trong quá trình Kiểm tra CNTT, vì nó cho phép hiệu quả phát hiện lỗi và cách ly trong quá trình sản xuất. Hiệu quả vị trí điểm kiểm tra là rất quan trọng để tối ưu hóa thiết kế PCB cho khả năng kiểm tra. Bằng cách theo dõi hướng dẫn DFM, các nhà thiết kế có thể xác định vị trí lý tưởng cho các điểm kiểm tra trên PCB, đảm bảo phạm vi phủ sóng lý tưởng và tạo điều kiện phát hiện lỗi.

Khoảng trống thích hợp giữa các thành phần và cạnh bo mạch cũng rất quan trọng để tạo điều kiện thuận lợi cho quá trình thử nghiệm. Các điểm kiểm tra được bố trí hợp lý cho phép kiểm tra nhanh chóng và chính xác, giúp cải thiện chất lượng sản phẩm tổng thể. Các yêu cầu kiểm tra CNTT cần được xem xét trong giai đoạn thiết kế để đảm bảo các điểm kiểm tra được đặt ở vị trí chiến lược để có phạm vi bao phủ tối đa.

Các câu hỏi thường gặp

Nguyên tắc thiết kế để kiểm thử là gì?

Các nguyên tắc thiết kế cho khả năng kiểm thử xoay quanh việc tạo mã mô-đun, liên kết lỏng lẻo và dễ kiểm tra. Điều này đạt được bằng cách tuân thủ các nguyên tắc như Trách nhiệm duy nhất, Mở/Đóng, Thay thế Liskov, Phân chia giao diện và Đảo ngược phụ thuộc.

Ngoài ra, hướng phát triển thử nghiệm, tái cấu trúc, Và giảm thiểu sự phụ thuộc là cần thiết để tạo mã có thể kiểm tra được. Bằng cách tuân theo các nguyên tắc này, các nhà phát triển có thể viết mã có thể bảo trì, có thể mở rộng và dễ kiểm tra, giúp cải thiện chất lượng mã và giảm nợ kỹ thuật.

Kỹ thuật DFT là gì?

Trong khi thiết kế PCB truyền thống tập trung vào tính thẩm mỹ và chức năng, thì cần phải thay đổi mô hình để ưu tiên khả năng kiểm tra.

Kỹ thuật DFT là một phương pháp thiết kế có chủ ý, tích hợp các cân nhắc thử nghiệm vào bố cục PCB. Những kỹ thuật này bao gồm việc đặt chiến lược điểm kiểm tra, sử dụng kỹ thuật quét ranh giới, và thực hiện tự kiểm tra tích hợp (BIST) khả năng.

Nguyên tắc PCB trong thử nghiệm là gì?

Hướng dẫn về PCB trong thử nghiệm nêu ra các yêu cầu cụ thể đối với vị trí điểm kiểm tra và giải phóng mặt bằng trên bố trí bảng mạch in. Những hướng dẫn này đảm bảo cách ly và kiểm tra lỗi hiệu quả trong quá trình sản xuất PCB, hợp lý hóa quy trình kiểm tra và cải thiện phát hiện lỗi.

Tại sao cần phải có DFT?

Thiết kế để kiểm tra (DFT) là một khía cạnh thiết yếu của thiết kế PCB. Nó cho phép hiệu quả phát hiện lỗi và cách ly trong quá trình sản xuất, giảm chi phí sản xuất và thời gian đưa sản phẩm ra thị trường. Bằng cách kết hợp các nguyên tắc DFT, nhà sản xuất có thể đảm bảo sản phẩm chất lượng cao, giảm thiểu khuyết tật và hợp lý hóa quy trình thử nghiệm.

Việc triển khai DFT hiệu quả tạo điều kiện cho việc xác định và giải quyết lỗi nhanh chóng. Điều này cuối cùng dẫn đến độ tin cậy của sản phẩm được cải thiện và sự hài lòng của khách hàng.