Thiết kế mạch tần số cao hiệu quả phụ thuộc vào việc tối ưu hóa độ dài đường dẫn tín hiệu, vị trí thành phần chiến lược, và điều khiển trở kháng dấu vết. Giảm thiểu độ dài đường dẫn tín hiệu làm giảm độ trễ truyền và suy giảm tín hiệu. Vị trí thành phần chiến lược giúp giảm thiểu nhiễu và đảm bảo tính toàn vẹn của tín hiệu, với các thành phần nhạy cảm được đặt cách xa nguồn nhiễu. Dấu vết trở kháng được kiểm soát ngăn chặn sự phản xạ và suy giảm tín hiệu. Bằng cách nắm vững những điều thiết yếu này mẹo bố trí, các nhà thiết kế có thể đạt được hiệu suất cao nhất trong thiết kế mạch tần số cao. Khi độ phức tạp của các mạch tần số cao tiếp tục phát triển, việc hiểu những nguyên tắc cơ bản này là điều cần thiết để đạt được hiệu suất mạch vượt trội.

Bài học chính

- Giảm thiểu độ dài đường dẫn tín hiệu để giảm độ trễ truyền và đảm bảo chất lượng cũng như độ tin cậy của tín hiệu trong các mạch tần số cao.

- Bố trí các thành phần một cách chiến lược để giảm thiểu nhiễu tín hiệu, giảm độ dài vết và tối ưu hóa đường dẫn tín hiệu cho các mạch tần số cao.

- Kiểm soát trở kháng vết bằng cách tính toán độ rộng vết dựa trên hằng số điện môi để ngăn phản xạ tín hiệu và đảm bảo tính toàn vẹn của tín hiệu.

- Đặt các thành phần nhạy cảm cách xa nguồn nhiễu và các thành phần tần số cao gần nhau hơn để giảm nhiễu và tối ưu hóa đường dẫn tín hiệu.

- Sử dụng các kỹ thuật bố trí thích hợp để tối ưu hóa vị trí thành phần và định tuyến tín hiệu, đảm bảo tính toàn vẹn của tín hiệu và giảm độ trễ trong các mạch tần số cao.

Tối ưu hóa độ dài đường dẫn tín hiệu

Khi thiết kế mạch tần số cao, giảm thiểu độ dài đường dẫn tín hiệu là cần thiết để ngăn chặn sự suy giảm tín hiệu và duy trì tính toàn vẹn tín hiệu. Trong Thiết kế PCB tần số cao, việc tối ưu hóa độ dài đường dẫn tín hiệu là rất quan trọng để đảm bảo truyền tín hiệu hiệu quả.

Chiều dài vết dài hơn có thể gây ra sự không phù hợp trở kháng, dẫn đến suy giảm tín hiệu và nhiễu. Để giảm thiểu điều này, nhà thiết kế PCB nên tập trung vào việc giảm thiểu độ dài đường dẫn tín hiệu để giảm độ trễ truyền tín hiệu.

Điều này có thể đạt được thông qua việc thực hiện đúng kỹ thuật bố trí, chẳng hạn như tối ưu hóa vị trí thành phần và định tuyến tín hiệu theo cách giảm thiểu độ dài dấu vết. Bằng cách đó, các nhà thiết kế có thể duy trì tính toàn vẹn của tín hiệu, giảm nhiễu và đảm bảo truyền tín hiệu đáng tin cậy.

Tối ưu hóa độ dài đường dẫn tín hiệu là rất quan trọng đối với hiệu suất mạch tần số cao vì nó ảnh hưởng trực tiếp đến chất lượng và độ tin cậy của tín hiệu. Bằng cách ưu tiên tối ưu hóa độ dài đường dẫn tín hiệu, các nhà thiết kế có thể tạo ra các mạch hiệu suất cao đáp ứng nhu cầu của các ứng dụng tần số cao hiện đại.

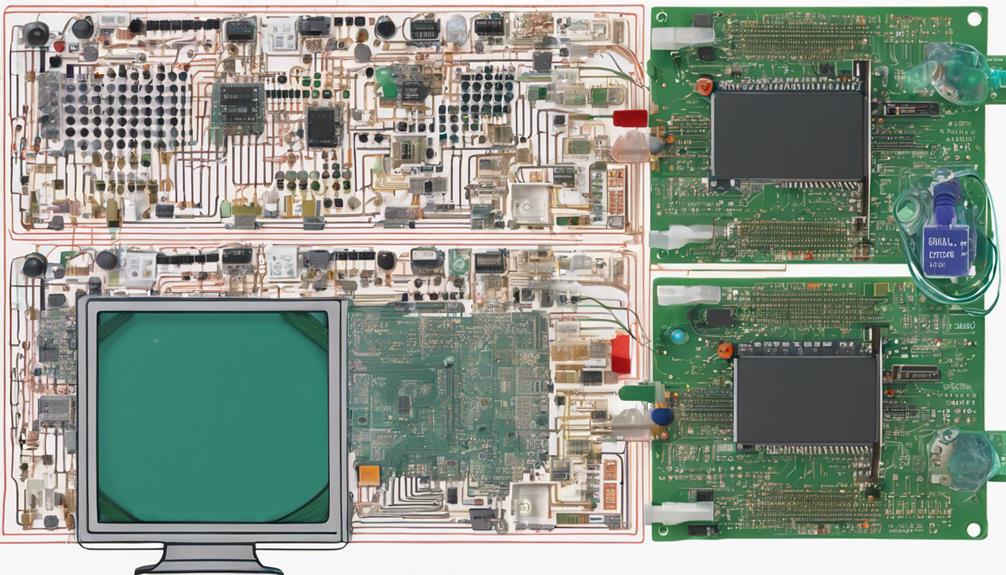

Vị trí thành phần chiến lược

Trong thiết kế mạch tần số cao, việc bố trí thành phần chiến lược là cần thiết vì nó cho phép giảm thiểu nhiễu tín hiệu và đảm bảo tính toàn vẹn của tín hiệu bằng cách giảm độ dài vết và độ trễ tín hiệu. Bằng cách sắp xếp cẩn thận các thành phần, các nhà thiết kế có thể tối ưu hóa đường dẫn tín hiệu, giảm độ dài đường truyền và giảm thiểu hiệu ứng điện dung và điện cảm ký sinh.

| Thành phần | Cân nhắc về vị trí | Những lợi ích |

|---|---|---|

| Linh kiện tần số cao | Đặt gần nhau hơn | Giảm nhiễu tín hiệu và độ dài đường truyền |

| Thành phần nhạy cảm | Đặt xa nguồn ồn | Giảm thiểu nhiễu tín hiệu và cải thiện chất lượng tín hiệu |

| Đường dẫn tín hiệu quan trọng | Tối ưu hóa vị trí thành phần cho đường dẫn ngắn nhất | Giảm độ trễ tín hiệu và cải thiện tính toàn vẹn tín hiệu |

Vị trí thành phần chiến lược là điều cần thiết trong thiết kế mạch tần số cao vì nó ảnh hưởng trực tiếp đến chất lượng và tính toàn vẹn của tín hiệu. Bằng cách giảm thiểu nhiễu tín hiệu và giảm độ dài đường truyền, các nhà thiết kế có thể đảm bảo truyền tín hiệu đáng tin cậy và duy trì tính toàn vẹn của tín hiệu. Bằng cách làm theo những nguyên tắc này, các nhà thiết kế có thể tạo ra các mạch tần số cao mang lại tín hiệu chất lượng cao và giảm thiểu nguy cơ nhiễu xuyên âm.

Kiểm soát trở kháng dấu vết

Quản lý trở kháng vết là điều cơ bản trong thiết kế mạch tần số cao vì nó ảnh hưởng trực tiếp đến sự phản xạ tín hiệu, truyền tải và hiệu suất tổng thể của mạch. Trong thiết kế PCB tần số cao, dấu vết trở kháng được kiểm soát là rất quan trọng để duy trì tính toàn vẹn của tín hiệu và giảm thiểu phản xạ tín hiệu. Để đạt được điều này, điều cần thiết là phải tính toán độ rộng vết phù hợp nhất dựa trên hằng số điện môi và trở kháng mong muốn.

Dưới đây là bốn cân nhắc chính để kiểm soát trở kháng vết:

- Trở kháng phù hợp: Đảm bảo rằng trở kháng của đường truyền phù hợp với trở kháng của các bộ phận và đường truyền để tránh phản xạ tín hiệu.

- Trở kháng dấu vết nhất quán: Duy trì trở kháng vết nhất quán trong toàn bộ bố cục để giảm suy giảm tín hiệu.

- Tính hằng số điện môi: Tính toán chiều rộng vết tốt nhất dựa trên hằng số điện môi của vật liệu PCB.

- Xác minh tính toàn vẹn tín hiệu: Xác nhận tính toàn vẹn của tín hiệu bằng cách mô phỏng mạch và phân tích sự phản xạ và truyền tín hiệu.

Các câu hỏi thường gặp

3 bước quan trọng hàng đầu trong quy trình thiết kế và bố trí PCB là gì?

Khi thiết kế bảng mạch in (PCB), ba bước chính sẽ phát huy hiệu suất vượt trội.

Đầu tiên, vị trí thành phần thích hợp là điều cần thiết để truyền tín hiệu hiệu quả và giảm thiểu nhiễu.

Thứ hai, định tuyến cẩn thận các đường truyền với trở kháng điều khiển duy trì tính toàn vẹn của tín hiệu và ngăn chặn sự phản xạ.

Quy tắc 3h trong thiết kế PCB là gì?

Các quy tắc 3h trong thiết kế PCB là hướng dẫn cơ bản cho bảng mạch tần số cao. Nó quy định rằng khoảng cách giữa các dấu hiệu tín hiệu tốc độ cao phải ít nhất gấp ba lần chiều cao của vật liệu điện môi giữa chúng.

Quy tắc này giúp ngăn ngừa nhiễu xuyên âm và nhiễu tín hiệu, đảm bảo phù hợp tính toàn vẹn tín hiệu và giảm thiểu rủi ro nhiễu điện từ. Tuân thủ quy tắc 3h là điều cần thiết để có hiệu suất vượt trội và hoạt động đáng tin cậy trong các thiết kế PCB tần số cao.

Làm thế nào để thiết kế một Pcb tần số cao?

Thiết kế PCB tần số cao đòi hỏi một cách tiếp cận tỉ mỉ để đảm bảo tính toàn vẹn tín hiệu và hiệu suất cao nhất. Không giống như các thiết kế tần số thấp, bố trí tần số cao yêu cầu xem xét cẩn thận độ dài dấu vết, điều khiển trở kháng, Và vị trí thành phần.

Để bắt đầu, hãy xác định các yêu cầu về dải tần và tín hiệu, sau đó chọn vật liệu và thiết kế xếp chồng phù hợp. Tiếp theo, tối ưu hóa vị trí thành phần, giảm thiểu đường dẫn tín hiệu và đảm bảo nối đất thích hợp.

Các quy tắc vàng của thiết kế PCB là gì?

Các quy tắc vàng của thiết kế PCB bao gồm các nguyên tắc thiết yếu để có được hiệu suất mạch lý tưởng. Những quy tắc này quy định việc giảm thiểu chiều dài dấu vết để giảm độ trễ và nhiễu tín hiệu, đảm bảo phù hợp vị trí mặt đất cho dòng trở về có trở kháng thấp và duy trì ổn định dấu vết trở kháng được kiểm soát để tránh hiện tượng méo và phản xạ tín hiệu.

Ngoài ra, khoảng cách thích hợp giữa các dấu vết tín hiệu tốc độ cao và các thành phần nhạy cảm là rất quan trọng để tránh nhiễu xuyên âm, cuối cùng đảm bảo chất lượng tuyệt vời. tính toàn vẹn tín hiệu và hiệu suất.