Designul pentru testabilitate este un aspect esențial al designului plăcilor de circuit imprimat (PCB), asigurând testarea eficientă, timpurie detectarea defecțiunii, și timp și resurse reduse pentru identificarea erorilor. Efectiv proiectare pentru testabilitate presupune implementarea puncte de testare strategic, menținerea spațiului liber și accesibilității și optimizarea rutarea semnalului. De asemenea, include utilizarea eficientă a vectorilor de testare, proiectarea pentru fabricabilitate și îmbunătățirea acoperirea și calitatea testelor. Urmând cele mai bune practici esențiale, designerii pot garanta o acoperire completă a testelor, pot reduce complexitatea testării și pot eficientiza producția. Pe măsură ce importanța testabilității continuă să crească, înțelegerea acestor principii devine din ce în ce mai importantă pentru proiectarea și fabricarea de succes a PCB-urilor.

Recomandări cheie

- Asigurați o acoperire completă a testelor prin încorporarea punctelor TIC pe fiecare rețea de proiectare și plasând strategic puncte de testare pentru accesibilitate.

- Implementați strategii de aranjare a PCB-ului care mențin distanța față de componente, spațiul liber la margini și plasarea strategică a punctelor de sondare pentru a reduce complexitatea testării.

- Proiectați pentru fabricabilitate prin plasarea punctelor ICT pe fiecare rețea de proiectare, asigurând puncte de testare accesibile cu o ștergere ușoară și respectând instrucțiunile DFT.

- Utilizați vectori de testare eficienți generați prin metode precum abordări pseudoaleatoare, exhaustive, inteligente și bazate pe constrângeri pentru a maximiza acoperirea defecțiunilor.

- Îmbunătățiți acoperirea și calitatea testelor prin încorporarea punctelor TIC, efectuând teste extinse și implementând teste unitare pentru a identifica rapid erorile de fabricație și defecțiunile componentelor.

Design pentru elementele fundamentale de testabilitate

Design for Testability (DFT) este un concept esențial în dezvoltarea de software și hardware care pune accent pe crearea de componente care promovează testarea ușoară, garantând astfel o mai bună calitate și fiabilitate a produsului final.

Încorporând principiile DFT, dezvoltatorii pot crea componente software care sunt favorabile diferite tipuri de testare, inclusiv testarea unitară, de integrare, funcțională, de încărcare și de performanță. Această abordare holistică a testării permite detectarea defecțiunilor și erorilor la începutul ciclului de dezvoltare, reducând probabilitatea problemelor în aval.

DFT eficientă ia în considerare întregul spectru de testare, asigurându-se că componentele sunt proiectate având în vedere capacitatea de testare. Această abordare facilitează izolarea rapidă a erorilor, reducerea timpului și a resurselor necesare pentru a identifica și rectifica erori de fabricație și defecțiuni ale componentelor.

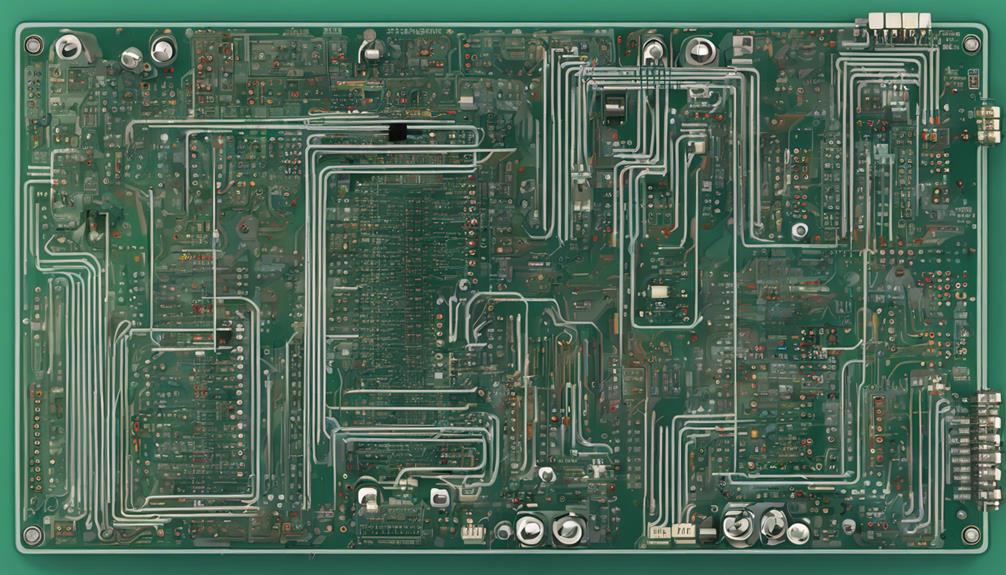

Aspect PCB pentru testabilitate maximă

Pentru o testare completă, configurațiile plăcilor de circuite imprimate (PCB) trebuie proiectate cu puncte de testare intenționate și caracteristici de accesibilitate care facilitează testarea eficientă și diagnosticarea defecțiunilor. Un aspect PCB bine conceput poate reduce foarte mult complexitatea și costul testării.

Pentru a obține o testabilitate maximă, trebuie urmate următoarele recomandări:

- Acoperire aprofundată a testului: Proiectați configurații PCB cu puncte ICT pe fiecare rețea pentru a garanta o acoperire completă a testelor.

- Distanța de la componente: Mențineți un spațiu minim de 50 mil între punctele de testare și componente și plăcuțe.

- Distanța la margine: Mențineți un spațiu liber de 100 mil între punctele de testare și marginea plăcii pentru accesibilitate.

- Amplasarea punctului sondei: Plasați strategic punctele de sondă pentru testarea manuală pentru a facilita accesul tehnicienilor.

Implementarea strategică a punctelor de testare

Punctele de testare poziționate strategic sunt esențiale pentru a garanta acoperirea completă a conexiunilor critice pe PCB, facilitând testarea eficientă și diagnosticarea defecțiunilor.

Prin încorporarea punctelor de testare în proiectarea PCB-ului, inginerii se pot asigura că testele unitare sunt detaliate, iar defecțiunile pot fi identificate și izolate rapid.

Pentru a obține o testabilitate ideală, punctele de testare ar trebui să fie plasate strategic, ținând cont de accesibilitate, degajare și cerințele de integritate a semnalului. Distanța adecvată între punctele de testare este, de asemenea, esențial pentru a preveni scurtcircuite și a asigura proceduri de testare fiabile.

În plus, punctele de testare poziționate în apropierea componentelor cheie permit eficiență izolarea defecțiunilor și depanarea în timpul testării.

Amplasarea eficientă a punctelor de testare nu numai că simplifică procesul de testare, ci și minimizează complexitatea dispozitivelor de testare, reducând costurile și timpul de testare.

Design testabil pentru fabricabilitate

Optimizarea configurațiilor PCB pentru fabricabilitate necesită un design testabil care să integreze puncte ICT pe fiecare rețea de proiectare pentru a garanta o acoperire completă a testelor și a facilita fluxurile de lucru eficiente de producție. Această abordare permite producătorilor contractuali (CM) să efectueze teste TIC, asigurându-se că ambele părți ale PCB sunt testate simultan.

Pentru a garanta testabilitatea eficientă, trebuie urmate următoarele recomandări:

- Puncte de testare accesibile: Garantați un spațiu liber de 50 mil pentru componente și plăcuțe pentru o accesibilitate ușoară.

- Plasament strategic: Poziționați punctele de testare pe baza ghidurilor DFT pentru a reduce complexitatea dispozitivului de fixare și potențialele costuri suplimentare.

- Testare manuală ușoară: Plasați punctele de sondă pentru a fi ușor accesibile de către tehnicieni.

- Testare coordonată: Colaborează cu CM pentru a coordona testarea TIC pentru fluxuri de lucru eficiente de producție.

Utilizarea eficientă a vectorilor de testare

În domeniul proiectare pentru testabilitate, utilizarea eficientă a vectorilor de testare este vitală pentru a garanta testarea amănunțită a funcționalității unui circuit.

Pentru a realiza acest lucru, este esențial să se utilizeze metode eficiente de generare a vectorilor care pot produce un set divers de vectori de testare, optimizând astfel acoperire de testare.

Metode de generare a vectorilor

Adesea, eficiența proiectării pentru testabilitate se bazează în mare măsură pe generarea eficientă a vectorilor de testare, care sunt esențiali pentru verificarea comportamentului unui proiect testat (DUT).

În testarea unitară, vectorii de testare sunt modele de intrare utilizate pentru a verifica comportamentul unui DUT, iar generarea lor eficientă este esențială pentru acoperirea completă a funcționalității DUT.

Pentru a garanta o testare eficientă, diverși algoritmi pot fi folosiți pentru generarea vectorului de testare. Acestea includ:

- Generarea vectorului de test pseudo-aleatoriu, care echilibrează aleatoritatea și repetabilitatea pentru o testare eficientă.

- Generare exhaustivă de vectori de testare, care implică generarea tuturor tiparelor de intrare posibile.

- Generare inteligentă de vectori, care optimizează acoperirea testelor minimizând în același timp timpul și resursele de testare.

- Generarea vectorului de testare bazat pe constrângeri, care generează vectori de testare pe baza constrângerilor specifice și a ghidurilor de testare.

Optimizarea acoperirii testelor

Optimizarea acoperirii testelor

Selecția strategică a punctelor de testare este esențială pentru maximizarea acoperirii defecțiunilor în testarea PCB, deoarece permite utilizarea eficientă a vectorilor de testare pentru a viza zone specifice ale designului testat. Această abordare garantează că defectele potențiale sunt identificate și abordate, reducând riscul PCB-urilor defecte. Alocarea corectă a vectorilor de testare poate reduce foarte mult timpul de testare, asigurând în același timp o acoperire completă.

| Tehnici de optimizare | Beneficii |

|---|---|

| Testarea de scanare a limitelor | Eficiență îmbunătățită a vectorului de testare prin accesarea nodurilor interne |

| Testați reutilizarea vectorului | Timp redus de testare și alocare îmbunătățită a resurselor |

| Testare orientată spre defecte | Testarea țintită a zonelor cu probabilitate mare de defecțiune |

| Testare bazată pe ATPG | Acoperire eficientă a erorilor cu generarea automată a modelelor de testare |

| Testarea hibridă | Combinarea diferitelor tehnici pentru o acoperire cuprinzătoare |

Simplificarea proiectării circuitelor complexe

Descompunerea circuitelor complicate în componente mai mici și mai ușor de gestionat este un pas esențial în simplificarea proiectării circuitelor complexe. Acest lucru le permite designerilor să abordeze fiecare modul în mod individual, sporind testabilitatea generală. Această abordare permite designerilor să se concentreze pe module specifice, reducând complexitatea designului general.

Pentru a realiza acest lucru, designerii pot folosi mai multe strategii:

- Design modular: Descompunerea circuitelor complexe în module reutilizabile promovează testarea și întreținerea mai ușoare.

- Reduceți dependențele: Minimizarea dependențelor dintre componente simplifică proiectarea și îmbunătățește izolarea defecțiunilor.

- Documentație clară: Furnizarea de documentație concisă și clară a proiectelor de circuite complexe facilitează înțelegerea și testarea funcționalității designului.

- Modele de design: Implementarea modelelor de proiectare, cum ar fi modelul Observer, poate simplifica interacțiunile complexe ale circuitelor și poate îmbunătăți testabilitatea.

Dirijarea eficientă a semnalului pentru testare

Când proiectați pentru testabilitate, eficient rutarea semnalului este esențial de garantat măsurători precise, iar o strategie de rutare a semnalului bine planificată poate reduce foarte mult erorile și poate îmbunătăți testarea eficienței.

Pentru a realiza acest lucru, este important să minimizați lungimea semnalului pentru a asigura măsurători precise. Mai mult, perechile de semnale diferențiale ar trebui direcționate împreună pentru a menține integritatea semnalului în timpul testării. Acest lucru previne degradarea semnalului si asigura rezultate fiabile ale testelor.

În plus, este vital să evitați rutarea semnalelor în apropierea componentelor zgomotoase pentru a preveni interferențele în timpul testării. Urme de impedanță controlate ar trebui utilizat pentru a menține integritatea și acuratețea semnalului în timpul testării. Acest lucru asigură că semnalele de testare nu sunt distorsionate, oferind rezultate fiabile ale testului.

Implementarea punctelor de testare în locații strategice este, de asemenea, esențială pentru acces ușor și procese de testare eficiente. Prin încorporarea acestora considerente de proiectare, designerii se pot asigura că strategia lor de rutare a semnalului este optimizată pentru testabilitate, rezultând testarea eficientă și precisă.

Dirijarea eficientă a semnalului este un aspect critic al proiectării pentru testabilitate și, urmând aceste bune practici, proiectanții pot asigura testare fiabilă și eficientă.

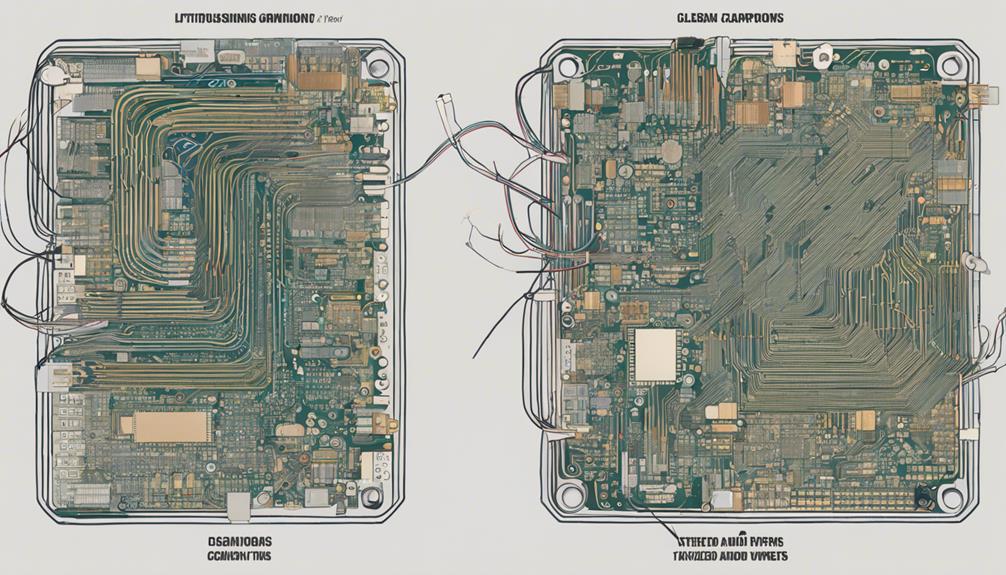

Proiectare pentru testarea în circuit

La proiectarea plăcilor de circuite imprimate (PCB) pentru testarea în circuit (ICT), trebuie să se acorde o atenție deosebită amplasării componentelor, identificării puncte de testare, și rutarea semnalului pentru a garanta testarea eficientă și eficientă. Prin optimizarea acestor factori, designerii pot facilita acoperirea TIC și izolarea rapidă a defecțiunilor, reducând în cele din urmă costurile de producție și îmbunătățind calitatea produsului.

În secțiunile următoare, vom examina puncte cheie privind amplasarea accesibilă a componentelor, identificarea punctelor de testare și considerațiile de rutare a semnalului care permit TIC de succes.

Plasare accesibilă a componentelor

Amplasarea corectă accesibilă a componentelor este esențială în proiectarea pentru testarea în circuit, deoarece permite amplasarea eficientă a punctelor de testare și garantează o acoperire completă a testului. Acest lucru este esențial pentru testarea unitară, deoarece asigură că codul de proiectare poate fi testat cuprinzător.

În testarea TIC, punctele de testare sunt plasate strategic pentru a facilita accesul ușor pentru echipamentele și tehnicienii de testare, reducând complexitatea testării.

Pentru a obține plasarea ideală a componentelor, designerii ar trebui să ia în considerare următoarele linii directoare:

- Cerințe de autorizare: Asigurați un spațiu liber de 50 mil la componente și un spațiu liber de 100 mil până la marginea plăcii.

- Plasarea punctului de testare: Localizați strategic punctele de testare pe configurația PCB, luând în considerare cerințele de degajare pentru o testare eficientă.

- Accesibilitatea componentelor: Asigurați-vă că componentele sunt accesibile în scopuri de testare, reducând complexitatea testării.

- Acoperire eficientă a testului: Garantați o acoperire completă a testelor prin plasarea punctelor de testare într-un mod care să permită testarea completă.

Identificarea punctului de testare

În căutarea unor teste eficiente în circuit, identificarea punctului de testare joacă un rol esențial în proiectarea PCB, deoarece permite plasarea strategică a punctelor dedicate pe placă pentru TIC. Această plasare deliberată a puncte de testare TIC asigură că acestea sunt ușor accesibile, cu un spațiu suficient față de componente și marginile plăcii, permițând testare eficientă în timpul producției.

Distanțarea adecvată între punctele de testare este, de asemenea, esențială, deoarece asigură o testare precisă și eficientă. Aceste puncte de testare facilitează conectarea dispozitive TIC, permițând procese automate de testare.

În plus, punctele de testare bine plasate și etichetate permit rapiditatea izolare greșită și depanare în timpul TIC, facilitând identificarea și rectificarea problemelor. Identificarea eficientă a punctelor de testare în proiectarea PCB este crucială pentru testarea eficientă în circuit, eficientizarea procesului de testare și reducerea timpului de producție.

Considerații privind rutarea semnalului

Considerațiile privind rutarea semnalului joacă un rol esențial în proiectarea pentru testarea în circuit, deoarece influențează direct acuratețea și fiabilitatea rezultatelor testelor. Dirijarea corectă a semnalului este esențială pentru a asigura testarea eficientă a PCB-urilor. În TIC, lungimile căilor semnalului ar trebui reduse la minimum, iar rutarea cu impedanță controlată ar trebui utilizată pentru a preveni degradarea semnalului.

Pentru a realiza o testare fiabilă, trebuie luate în considerare următoarele considerații privind rutarea semnalului:

- Minimizați încrucișările: Evitați încrucișarea semnalelor unul peste altul pentru a preveni interferențele electromagnetice și degradarea semnalului.

- Evitați curbele ascuțite: Folosiți trasee netede, curbate pentru a preveni reflexiile și radiațiile semnalului.

- Limitați vias: Minimizați utilizarea vias-urilor pentru a preveni pierderea și degradarea semnalului.

- Plasarea strategică a punctului de testare: Plasați punctele de testare strategic pentru a facilita accesul ușor pentru sondele de testare, asigurând testarea eficientă și fiabilă.

Îmbunătățirea acoperirii și calității testelor

Strategii de testare eficiente, cum ar fi încorporând puncte TIC pe fiecare plasă de proiectare, sunt vitale pentru garantare acoperire amănunțită a testului și calitate în fabricarea PCB. Această abordare permite teste ample, reducând probabilitatea ca erorile de fabricație și defecțiunile componentelor să nu fie detectate.

Prin includerea punctelor de testare cu o distanță adecvată față de componente și marginea plăcii, tehnicienii pot conduce eficient testarea unitară și identificați prompt problemele. În plus, TIC poate fi condusă simultan de ambele părți ale consiliului de bord, cu coordonarea producătorului contractual, simplificând procesul de testare.

În plus, având puncte de sondă ușor accesibile pentru testarea manuală simplifică procedurile de testare, reducând riscul erorii umane. Acoperirea testelor critice și asigurarea calității sunt esențiale în identificarea promptă a erorilor de fabricație și a defecțiunilor componentelor, asigurându-se că numai PCB-uri de înaltă calitate sunt scoase pe piata.

Optimizarea designului PCB pentru testare

Când optimizați designul PCB pentru testare, este vital să luați în considerare amplasarea puncte de testare, asigurându-se că acestea sunt ușor accesibile pentru testare eficientă.

Amplasarea corectă a punctului de testare facilitează minuțiozitatea acoperire de testare, reduce timpul de testare și mărește calitatea testului.

Design pentru accesibilitate

Un aspect PCB bine conceput, care încorporează puncte de testare accesibile, permite procese de testare eficiente, reducând timpul și costurile asociate cu identificarea și remedierea defectelor. Proiectarea pentru accesibilitate este un aspect critic al optimizării designului PCB pentru testare, deoarece facilitează procesul de testare și asigură o acoperire completă a defecțiunilor.

Pentru a obține accesibilitatea ideală, designerii ar trebui să ia în considerare următorii factori cheie:

- Distanță față de componente și marginile plăcii: Asigurați-vă că punctele de testare au suficient spațiu liber pentru a permite accesul ușor pentru sondele de testare.

- Puncte TIC pe fiecare rețea de proiectare: Încorporați puncte ICT pe fiecare rețea de proiectare pentru a permite o acoperire completă a testelor în timpul producției.

- Colaborare cu producatorii contractuali: Colaborați cu producătorii contractuali pentru a determina cele mai eficiente metodologii de testare și modificări ale dispozitivelor de fixare pentru o acoperire îmbunătățită a defecțiunilor.

- Testarea TIC pentru feedback imediat: Utilizați testarea TIC pentru a primi feedback imediat cu privire la erorile de fabricație, defecțiunile componentelor și funcționalitatea generală a PCB-ului, permițând ajustări rapide.

Plasarea punctului de testare

Plasarea strategică a punctelor de testare pe un PCB este esențială pentru o acoperire maximă în timpul testarea TIC, deoarece permite eficient detectarea defecțiunii și izolarea în timpul producției. Efectiv plasarea punctului de testare este critic pentru optimizare Design PCB pentru testabilitate. Urmărind Ghidurile DFM, designerii pot determina locațiile ideale pentru punctele de testare pe PCB, asigurând o acoperire ideală și facilitând detectarea defecțiunilor.

Distanța adecvată față de componente și marginile plăcii este, de asemenea, vitală pentru a facilita procesele de testare. Punctele de testare bine plasate permit testarea rapidă și precisă, ceea ce duce la îmbunătățirea calității generale a produsului. Cerințele de testare TIC ar trebui luate în considerare în timpul fazei de proiectare pentru a se asigura că punctele de testare sunt plasate strategic pentru o acoperire maximă.

întrebări frecvente

Care sunt principiile de proiectare pentru testabilitate?

Principiile de proiectare pentru testabilitate se învârt în jurul codului de elaborare, adică modulare, slab cuplat și ușor de testat. Acest lucru se realizează prin aderarea la principii precum responsabilitatea unică, deschis/închis, înlocuirea Liskov, segregarea interfeței și inversarea dependenței.

În plus, dezvoltare bazată pe teste, refactorizarea, și minimizarea dependențelor sunt esențiale pentru crearea codului testabil. Urmând aceste principii, dezvoltatorii pot scrie cod care poate fi întreținut, scalabil și ușor de testat, rezultând o calitate îmbunătățită a codului și o datorie tehnică redusă.

Ce sunt tehnicile DFT?

În timp ce designul PCB tradițional se concentrează pe estetică și funcționalitate, este necesară o schimbare de paradigmă pentru a acorda prioritate testabilității.

Tehnicile DFT sunt o abordare de proiectare deliberată care integrează considerațiile de testare în aspectul PCB. Aceste tehnici includ plasarea strategică puncte de testare, folosind tehnici de scanare a limitelor, și implementare autotest încorporat (BIST).

Care sunt orientările PCB în testare?

Orientările PCB în testare conturează cerințe specifice pentru plasarea punctului de testare și clearance-ul pe dispozițiile plăcilor de circuite imprimate. Aceste linii directoare garantează izolarea eficientă a defecțiunilor și testarea în timpul fabricării PCB-ului, simplificând procesul de testare și îmbunătățind detectarea defecțiunii.

De ce este necesar DFT?

Design for Testability (DFT) este un aspect esențial al designului PCB. Acesta permite eficient detectarea defecțiunii și izolarea în timpul producției, reducând costurile de producție și timpul de lansare pe piață. Încorporând principiile DFT, producătorii pot garanta produse de înaltă calitate, minimizați defectele și simplificați procesele de testare.

Implementarea eficientă a DFT facilitează identificarea și rezolvarea rapidă a defecțiunilor. Acest lucru duce în cele din urmă la o fiabilitate îmbunătățită a produsului și la satisfacția clienților.