Ontwerpen voor testbaarheid is een essentieel aspect van het ontwerp van printplaten (PCB's), en zorgt voor efficiënt testen, vroege fout detectieen minder tijd en middelen voor het identificeren van fouten. Effectief ontwerp voor testbaarheid impliceert de uitvoering ervan testpunten strategisch, het handhaven van de speling en toegankelijkheid, en het optimaliseren signaal routering. Het omvat ook het efficiënt gebruiken van testvectoren, het ontwerpen met het oog op maakbaarheid en het verbeteren ervan testdekking en kwaliteit. Door essentiële best practices te volgen, kunnen ontwerpers een grondige testdekking garanderen, de testcomplexiteit verminderen en de productie stroomlijnen. Naarmate het belang van testbaarheid blijft groeien, wordt het begrijpen van deze principes steeds belangrijker voor succesvol PCB-ontwerp en -productie.

Belangrijkste leerpunten

- Zorg voor een grondige testdekking door ICT-punten op te nemen in elk ontwerpnetwerk en testpunten voor toegankelijkheid strategisch te plaatsen.

- Implementeer PCB-lay-outstrategieën die de afstand tot componenten, de randvrijheid en de strategische plaatsing van sondepunten behouden om de testcomplexiteit te verminderen.

- Ontwerp voor maakbaarheid door ICT-punten op elk ontwerpnet te plaatsen, te zorgen voor toegankelijke testpunten met gemakkelijke toegang en door de DFT-richtlijnen te volgen.

- Gebruik efficiënte testvectoren die zijn gegenereerd via methoden als pseudo-willekeurige, uitputtende, intelligente en op beperkingen gebaseerde benaderingen om de foutdekking te maximaliseren.

- Verbeter de testdekking en -kwaliteit door ICT-punten op te nemen, uitgebreide tests uit te voeren en unit-tests te implementeren om productiefouten en componentfouten snel te identificeren.

Ontwerp voor de grondbeginselen van testbaarheid

Design for Testability (DFT) is een essentieel concept in de software- en hardwareontwikkeling dat de nadruk legt op het creëren van componenten die eenvoudig testen bevorderen, waardoor een betere kwaliteit en betrouwbaarheid van het eindproduct wordt gegarandeerd.

Door DFT-principes te integreren, kunnen ontwikkelaars softwarecomponenten creëren die bevorderlijk zijn voor verschillende soorten testen, inclusief unit-, integratie-, functionele, belasting- en prestatietesten. Deze holistische benadering van testen maakt het mogelijk om detectie van fouten en fouten vroeg in de ontwikkelingscyclus, waardoor de kans op problemen stroomafwaarts kleiner wordt.

Effectieve DFT houdt rekening met het hele testspectrum en zorgt ervoor dat componenten worden ontworpen met testbaarheid in gedachten. Deze aanpak vergemakkelijkt snelle foutisolatie, het verminderen van de tijd en middelen verplicht te identificeren en te corrigeren productiefouten en defecten aan componenten.

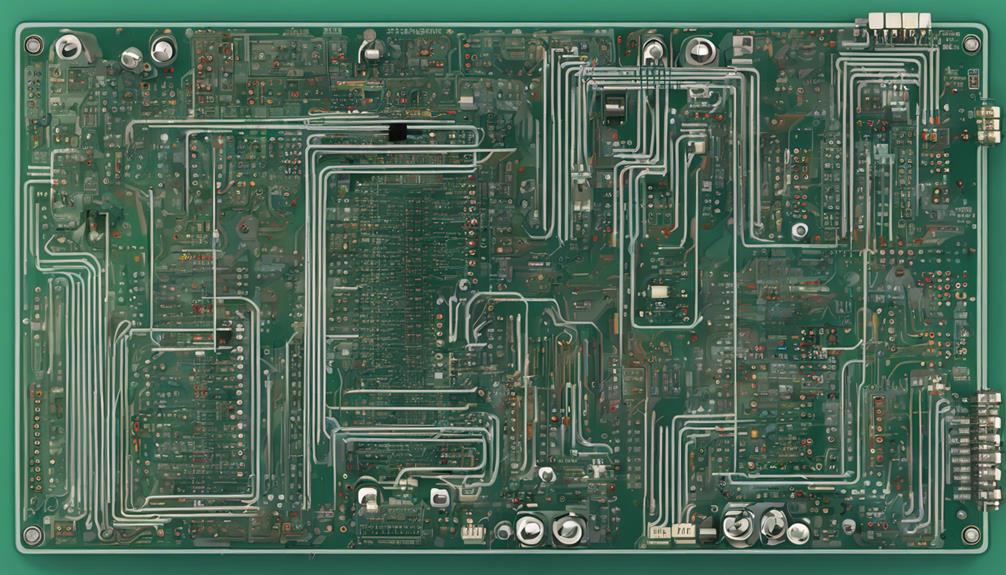

PCB-indeling voor maximale testbaarheid

Voor een grondige testbaarheid moeten lay-outs van printplaten (PCB's) worden ontworpen met opzettelijke testpunten en toegankelijkheidsfuncties die efficiënt testen en foutdiagnose vergemakkelijken. Een goed ontworpen PCB-layout kan de complexiteit en kosten van testen aanzienlijk verminderen.

Om maximale testbaarheid te bereiken, moeten de volgende richtlijnen worden gevolgd:

- Grondige testdekking: Ontwerp PCB-lay-outs met ICT-punten op elk net om een grondige testdekking te garanderen.

- Afstand tot componenten: Houd een minimale afstand van 50 mil aan tussen de testpunten, componenten en remblokken.

- Randvrijheid: Zorg voor een afstand van 100 mil tussen de testpunten en de rand van het bord, zodat de punten goed bereikbaar zijn.

- Plaatsing van sondepunten: Strategisch plaatsen van sondepunten voor handmatig testen om gemakkelijke toegang voor technici te vergemakkelijken.

Testpunten strategisch implementeren

Strategisch gepositioneerde testpunten zijn essentieel om een grondige dekking van kritische verbindingen op de printplaat te garanderen, wat het mogelijk maakt efficiënt testen en foutdiagnose.

Door testpunten in het PCB-ontwerp op te nemen, kunnen ingenieurs ervoor zorgen dat de unit-tests gedetailleerd zijn en dat fouten snel kunnen worden geïdentificeerd en geïsoleerd.

Om een ideale testbaarheid te bereiken, moeten testpunten strategisch worden geplaatst, waarbij rekening moet worden gehouden met toegankelijkheid, vrije ruimte en vereisten voor signaalintegriteit. Juiste afstand tussen de testpunten is ook van cruciaal belang om kortsluiting te voorkomen en te garanderen betrouwbare testprocedures.

Bovendien maken testpunten die in de buurt van belangrijke componenten zijn geplaatst een efficiënte werking mogelijk Foutisolatie en probleemoplossing tijdens het testen.

Effectieve plaatsing van testpunten vereenvoudigt niet alleen het testproces, maar minimaliseert ook de complexiteit van de testopstellingen, waardoor de hoeveelheid werk wordt verminderd testkosten en tijd.

Testbaar ontwerp voor maakbaarheid

Het optimaliseren van PCB-lay-outs voor produceerbaarheid vereist een testbaar ontwerp dat ICT-punten op elk ontwerpnet integreert om een grondige testdekking te garanderen en efficiënte productieworkflows te vergemakkelijken. Deze aanpak stelt contractfabrikanten (CM's) in staat ICT-tests uit te voeren, zodat beide zijden van de PCB gelijktijdig worden getest.

Om een effectieve testbaarheid te garanderen, moeten de volgende richtlijnen worden gevolgd:

- Toegankelijke testpunten: Garandeer een ruimte van 50 mil voor componenten en remblokken voor gemakkelijke toegankelijkheid.

- Strategische plaatsing: Positioneer testpunten op basis van DFT-richtlijnen om de complexiteit van de armatuur en mogelijke extra kosten te verminderen.

- Eenvoudig handmatig testen: Plaats sondepunten voor gemakkelijke toegankelijkheid voor technici.

- Gecoördineerd testen: Samenwerken met de CM om ICT-testen te coördineren voor efficiënte productieworkflows.

Efficiënt gebruik van testvectoren

Op het domein van ontwerp voor testbaarheidis het efficiënt gebruiken van testvectoren essentieel om een grondige test van de functionaliteit van een circuit te garanderen.

Om dit te bereiken is het essentieel om effectieve methoden voor het genereren van vectoren te gebruiken die een gevarieerde set testvectoren kunnen produceren, waardoor de dekking testen.

Methoden voor het genereren van vectoren

Vaak is de efficiëntie van het ontwerp op het gebied van testbaarheid sterk afhankelijk van het effectief genereren van testvectoren, die essentieel zijn voor het verifiëren van het gedrag van een te testen ontwerp (DUT).

Bij het testen van eenheden zijn testvectoren invoerpatronen die worden gebruikt om het gedrag van een DUT te verifiëren, en hun efficiënte generatie is van cruciaal belang voor een grondige dekking van de DUT-functionaliteit.

Om efficiënt testen te garanderen, kunnen verschillende algoritmen worden gebruikt voor het genereren van testvectoren. Deze omvatten:

- Pseudo-willekeurige generatie van testvectoren, dat willekeur en herhaalbaarheid in evenwicht brengt voor effectief testen.

- Uitputtende generatie van testvectoren, waarbij alle mogelijke invoerpatronen worden gegenereerd.

- Intelligente vectorgeneratie, waarmee de testdekking wordt geoptimaliseerd en de testtijd en middelen worden geminimaliseerd.

- Op beperkingen gebaseerde generatie van testvectoren, dat testvectoren genereert op basis van specifieke beperkingen en testbaarheidsrichtlijnen.

Testdekking optimaliseren

Testdekking optimaliseren

Strategische selectie van testpunten is essentieel voor het maximaliseren van de foutdekking bij PCB-testen, omdat het het efficiënte gebruik van testvectoren mogelijk maakt om specifieke gebieden van het te testen ontwerp te targeten. Deze aanpak garandeert dat potentiële defecten worden geïdentificeerd en aangepakt, waardoor het risico op defecte PCB's wordt verminderd. Een juiste toewijzing van testvectoren kan de testtijd aanzienlijk verkorten en tegelijkertijd een grondige dekking garanderen.

| Optimalisatietechnieken | Voordelen |

|---|---|

| Grensscan-testen | Verbeterde testvectorefficiëntie door toegang te krijgen tot interne knooppunten |

| Hergebruik van vector testen | Kortere testtijd en verbeterde toewijzing van middelen |

| Defectgerichte testen | Gericht testen van gebieden met een hoge foutkans |

| ATPG-gebaseerd testen | Efficiënte foutdekking met geautomatiseerde generatie van testpatronen |

| Hybride testen | Het combineren van verschillende technieken voor een uitgebreide dekking |

Vereenvoudiging van complex circuitontwerp

Het opsplitsen van ingewikkelde circuits in kleinere, beter beheersbare componenten is een essentiële stap in het vereenvoudigen van het complexe circuitontwerp. Hierdoor kunnen ontwerpers elke module afzonderlijk aanpakken, waardoor de algehele testbaarheid wordt vergroot. Deze aanpak stelt ontwerpers in staat zich te concentreren op specifieke modules, waardoor de complexiteit van het algehele ontwerp wordt verminderd.

Om dit te bereiken kunnen ontwerpers verschillende strategieën toepassen:

- Modulair ontwerp: Het opsplitsen van complexe circuits in herbruikbare modules bevordert eenvoudiger testen en onderhoud.

- Verminder afhankelijkheden: Het minimaliseren van afhankelijkheden tussen componenten vereenvoudigt het ontwerp en verbetert de foutisolatie.

- Duidelijke documentatie: Het verstrekken van beknopte en duidelijke documentatie van complexe circuitontwerpen vergemakkelijkt het begrijpen en testen van de functionaliteit van het ontwerp.

- Ontwerp patronen: Het implementeren van ontwerppatronen, zoals het Observer-patroon, kan complexe circuitinteracties vereenvoudigen en de testbaarheid verbeteren.

Effectieve signaalroutering voor testen

Bij het ontwerpen op testbaarheid, effectief signaal routering is essentieel om te garanderen nauwkeurige metingenen een goed geplande signaalrouteringsstrategie kan fouten aanzienlijk verminderen en de efficiëntie verbeteren. efficiëntie testen.

Om dit te bereiken is het belangrijk om de signaallengte te minimaliseren om nauwkeurige metingen te garanderen. Bovendien moeten differentiële signaalparen samen worden gerouteerd om ze te behouden signaalintegriteit tijdens het testen. Dit voorkomt signaalverslechtering en verzekert betrouwbare testresultaten.

Bovendien is het van cruciaal belang om te voorkomen dat signalen in de buurt van luidruchtige componenten worden geleid om interferentie tijdens het testen te voorkomen. Gecontroleerde impedantiesporen moet worden gebruikt om de signaalintegriteit en nauwkeurigheid tijdens het testen te behouden. Dit zorgt ervoor dat de testsignalen niet worden vervormd, wat betrouwbare testresultaten oplevert.

Het implementeren van testpunten op strategische locaties is ook van cruciaal belang voor gemakkelijke toegang en efficiënte testprocessen. Door deze in te bouwen Ontwerp Overwegingenkunnen ontwerpers ervoor zorgen dat hun signaalrouteringsstrategie is geoptimaliseerd voor testbaarheid, wat resulteert in efficiënte en nauwkeurige tests.

Effectieve signaalroutering is een cruciaal aspect van het ontwerp voor de testbaarheid, en door deze best practices te volgen, kunnen ontwerpers betrouwbare en efficiënte tests garanderen.

Ontwerpen voor testen in circuits

Bij het ontwerpen van printplaten (PCB's) voor in-circuit testen (ICT) moet zorgvuldig rekening worden gehouden met de plaatsing van componenten, identificatie van test punten, En signaal routering om efficiënt en effectief testen te garanderen. Door deze factoren te optimaliseren kunnen ontwerpers ICT-dekking en snelle foutisolatie faciliteren, waardoor uiteindelijk de productiekosten worden verlaagd en de productkwaliteit wordt verbeterd.

In de volgende paragrafen zullen we de belangrijkste punten van toegankelijke plaatsing van componenten, identificatie van testpunten en overwegingen voor signaalroutering die succesvolle ICT mogelijk maken.

Toegankelijke plaatsing van componenten

Een juiste toegankelijke plaatsing van componenten is essentieel bij het ontwerpen voor in-circuit testen, omdat het een efficiënte plaatsing van testpunten mogelijk maakt en een grondige testdekking garandeert. Dit is van cruciaal belang voor het testen van eenheden, omdat het ervoor zorgt dat de ontwerpcode uitgebreid kan worden getest.

Bij ICT-testen zijn testpunten strategisch geplaatst om gemakkelijke toegang voor testapparatuur en technici te vergemakkelijken, waardoor de testcomplexiteit wordt verminderd.

Om een ideale plaatsing van componenten te bereiken, moeten ontwerpers de volgende richtlijnen in acht nemen:

- Opruimingsvereisten: Zorg voor een speling van 50 mil tot de componenten en 100 mil tot de rand van het bord.

- Plaatsing van testpunten: Strategisch lokaliseren van testpunten op de PCB-lay-out, rekening houdend met de vereisten voor vrije ruimte voor efficiënt testen.

- Toegankelijkheid van componenten: Zorg ervoor dat componenten toegankelijk zijn voor testdoeleinden, waardoor de testcomplexiteit wordt verminderd.

- Efficiënte testdekking: Garandeer een grondige testdekking door testpunten zo te plaatsen dat uitgebreide tests mogelijk zijn.

Identificatie van testpunten

Bij het nastreven van efficiënte tests in circuits, identificatie van testpunten speelt een cruciale rol bij het PCB-ontwerp, omdat het de strategische plaatsing van speciale punten op het bord voor ICT mogelijk maakt. Deze bewuste plaatsing van ICT-testpunten zorgt ervoor dat ze gemakkelijk toegankelijk zijn, met voldoende afstand tot componenten en plaatranden efficiënt testen tijdens de productie.

De juiste afstand tussen testpunten is ook essentieel, omdat het zorgt voor nauwkeurige en efficiënte tests. Deze testpunten vergemakkelijken de verbinding van ICT-armaturen, waardoor geautomatiseerde testprocessen mogelijk zijn.

Bovendien maken goed geplaatste en gelabelde testpunten een snelle test mogelijk foutisolatie En debuggen tijdens ICT, waardoor de identificatie en rectificatie van problemen wordt vergemakkelijkt. Effectieve testpuntidentificatie bij PCB-ontwerp is cruciaal voor efficiënt testen in circuits, het stroomlijnen van het testproces en het verkorten van de productietijd.

Overwegingen bij signaalroutering

Overwegingen voor signaalroutering spelen een cruciale rol bij het ontwerpen voor in-circuit testen, omdat ze rechtstreeks van invloed zijn op de nauwkeurigheid en betrouwbaarheid van testresultaten. Een goede signaalroutering is essentieel voor het efficiënt testen van PCB's. In ICT moeten signaalpadlengtes worden geminimaliseerd en moet gecontroleerde impedantieroutering worden gebruikt om signaalverslechtering te voorkomen.

Om betrouwbare tests te realiseren, moet rekening worden gehouden met de volgende overwegingen bij signaalroutering:

- Minimaliseer cross-overs: Vermijd het kruisen van signalen over elkaar om elektromagnetische interferentie en signaalverslechtering te voorkomen.

- Vermijd scherpe bochten: Gebruik gladde, gebogen routes om signaalreflecties en straling te voorkomen.

- Beperk via's: Minimaliseer het gebruik van via's om signaalverlies en degradatie te voorkomen.

- Strategische plaatsing van testpunten: Plaats testpunten strategisch om gemakkelijke toegang voor testsondes te vergemakkelijken, waardoor efficiënt en betrouwbaar testen wordt gegarandeerd.

Verbetering van de dekking en kwaliteit van tests

Effectieve teststrategieën, zoals ICT-punten inbouwen op elk designnet, zijn essentieel voor het garanderen grondige testdekking en kwaliteit in de PCB-productie. Deze aanpak maakt het mogelijk uitgebreide testen, waardoor de kans kleiner wordt dat productiefouten en defecten aan componenten onopgemerkt blijven.

Door testpunten op te nemen met voldoende afstand tot de componenten en de rand van het bord, kunnen technici efficiënt uitvoeren testen van een eenheid en problemen snel identificeren. Bovendien kan ICT gelijktijdig aan beide kanten van het bestuur worden uitgevoerd, onder coördinatie van de contractfabrikant, waardoor het testproces wordt gestroomlijnd.

Bovendien vereenvoudigt het hebben van gemakkelijk toegankelijke meetpunten voor handmatig testen de testprocedures, waardoor het risico op menselijke fouten wordt verminderd. Kritische testdekking en kwaliteitsborging zijn essentieel om productiefouten en componentstoringen snel te identificeren, zodat alleen hoogwaardige PCB's worden op de markt gebracht.

PCB-ontwerp optimaliseren voor testen

Bij het optimaliseren van het PCB-ontwerp voor testen is het van cruciaal belang om rekening te houden met de plaatsing van de printplaten test punten, zodat ze gemakkelijk toegankelijk zijn voor efficiënt testen.

Een juiste plaatsing van de testpunten maakt een grondige test mogelijk dekking testen, verkort de testtijd en verhoogt de testkwaliteit.

Ontwerp voor toegankelijkheid

Een goed ontworpen PCB-indeling met toegankelijke testpunten maakt efficiënte testprocessen mogelijk, waardoor de tijd en kosten die gepaard gaan met het identificeren en verhelpen van defecten worden verminderd. Ontwerp voor toegankelijkheid is een cruciaal aspect bij het optimaliseren van PCB-ontwerp voor testen, omdat het het testproces vergemakkelijkt en een grondige foutdekking garandeert.

Om een ideale toegankelijkheid te bereiken, moeten ontwerpers rekening houden met de volgende sleutelfactoren:

- Afstand tot componenten en plaatranden: Zorg ervoor dat de testpunten voldoende ruimte hebben om gemakkelijke toegang voor de testsondes mogelijk te maken.

- ICT-punten op elk ontwerpnet: Integreer ICT-punten op elk ontwerpnet om grondige testdekking tijdens de productie mogelijk te maken.

- Samenwerking met contractfabrikanten: Werk samen met contractfabrikanten om de meest effectieve testmethoden en armatuuraanpassingen te bepalen voor een betere foutdekking.

- ICT-testen voor directe feedback: Maak gebruik van ICT-testen om onmiddellijke feedback te krijgen over productiefouten, defecten aan componenten en de algehele PCB-functionaliteit, waardoor snelle aanpassingen mogelijk zijn.

Plaatsing van testpunten

Het strategisch plaatsen van testpunten op een PCB is essentieel voor maximale dekking tijdens ICT-testen, omdat het efficiënt werkt fout detectie en isolatie tijdens de productie. Effectief plaatsing van testpunten is van cruciaal belang voor het optimaliseren PCB-ontwerp voor testbaarheid. Door te volgen DFM-richtlijnenkunnen ontwerpers de ideale locaties voor testpunten op de printplaat bepalen, waardoor een ideale dekking wordt gegarandeerd en foutdetectie wordt vergemakkelijkt.

De juiste afstand tot componenten en bordranden is ook van cruciaal belang om testprocessen te vergemakkelijken. Goed geplaatste testpunten maken snelle en nauwkeurige tests mogelijk, wat leidt tot een betere algehele productkwaliteit. Tijdens de ontwerpfase moeten ICT-testvereisten in overweging worden genomen om ervoor te zorgen dat testpunten strategisch worden geplaatst voor maximale dekking.

Veel Gestelde Vragen

Wat zijn de principes van ontwerp voor testbaarheid?

De principes van ontwerp voor testbaarheid draaien om het maken van code modulair, losjes gekoppeld en gemakkelijk te testen. Dit wordt bereikt door het naleven van principes als Single Responsibility, Open/Closed, Liskov Substitution, Interface Segregation en Dependency Inversion.

Aanvullend, test gedreven ontwikkeling, refactoring, En het minimaliseren van afhankelijkheden zijn essentieel voor het maken van testbare code. Door deze principes te volgen, kunnen ontwikkelaars code schrijven die onderhoudbaar, schaalbaar en gemakkelijk te testen is, wat resulteert in een verbeterde codekwaliteit en minder technische schulden.

Wat zijn DFT-technieken?

Terwijl traditioneel PCB-ontwerp zich richt op esthetiek en functionaliteit, is een paradigmaverschuiving nodig om prioriteit te geven aan testbaarheid.

DFT-technieken zijn een doelbewuste ontwerpaanpak die testoverwegingen integreert in de PCB-indeling. Deze technieken omvatten strategisch plaatsen test punten, gebruik makend van technieken voor grensscans, en implementeren ingebouwde zelftest (BIST)-mogelijkheden.

Wat zijn PCB-richtlijnen bij testen?

PCB-richtlijnen bij het testen schetsen specifieke vereisten voor plaatsing van testpunten en speling op printplaatlay-outs. Deze richtlijnen garanderen een efficiënte foutisolatie en testen tijdens de PCB-productie, waardoor het testproces wordt gestroomlijnd en verbeterd fout detectie.

Waarom is DFT vereist?

Design for Testability (DFT) is een essentieel aspect van PCB-ontwerp. Het maakt efficiënt fout detectie en isolatie tijdens de productie, waardoor de productiekosten en de time-to-market worden verlaagd. Door DFT-principes op te nemen, kunnen fabrikanten garanderen kwalitatief hoogwaardige producten, minimaliseer defecten en stroomlijn testprocessen.

Effectieve DFT-implementatie vergemakkelijkt een snelle identificatie en oplossing van fouten. Dit leidt uiteindelijk tot een verbeterde productbetrouwbaarheid en klanttevredenheid.