Reka bentuk untuk kebolehujian adalah aspek penting dalam reka bentuk papan litar bercetak (PCB), memastikan ujian yang cekap, lebih awal pengesanan kesalahan, dan mengurangkan masa dan sumber untuk mengenal pasti ralat. Berkesan reka bentuk untuk kebolehujian melibatkan pelaksanaan mata ujian secara strategik, mengekalkan kelegaan dan kebolehaksesan, dan mengoptimumkan penghalaan isyarat. Ia juga termasuk menggunakan vektor ujian dengan cekap, mereka bentuk untuk kebolehkilangan dan meningkatkan liputan dan kualiti ujian. Dengan mengikuti amalan terbaik yang penting, pereka boleh menjamin liputan ujian menyeluruh, mengurangkan kerumitan ujian dan memperkemas pengeluaran. Memandangkan kepentingan kebolehujian terus berkembang, pemahaman prinsip ini menjadi semakin penting untuk reka bentuk dan pembuatan PCB yang berjaya.

Pengambilan Utama

- Pastikan liputan ujian menyeluruh dengan memasukkan mata ICT pada setiap jaringan reka bentuk dan meletakkan titik ujian secara strategik untuk kebolehcapaian.

- Laksanakan strategi susun atur PCB yang mengekalkan kelegaan daripada komponen, kelegaan tepi dan penempatan titik probe strategik untuk mengurangkan kerumitan ujian.

- Reka bentuk untuk kebolehkilangan dengan meletakkan titik ICT pada setiap jaringan reka bentuk, memastikan titik ujian boleh diakses dengan pelepasan mudah, dan mengikuti garis panduan DFT.

- Gunakan vektor ujian cekap yang dijana melalui kaedah seperti pendekatan pseudo-rawak, menyeluruh, pintar dan berasaskan kekangan untuk memaksimumkan liputan kerosakan.

- Meningkatkan liputan dan kualiti ujian dengan menggabungkan mata ICT, menjalankan ujian yang meluas, dan melaksanakan ujian unit untuk mengenal pasti ralat pembuatan dan kegagalan komponen dengan segera.

Reka Bentuk untuk Asas Kebolehujian

Design for Testability (DFT) ialah konsep penting dalam pembangunan perisian dan perkakasan yang menekankan penciptaan komponen yang menggalakkan ujian mudah, dengan itu menjamin kualiti dan kebolehpercayaan yang lebih baik bagi produk akhir.

Dengan menggabungkan prinsip DFT, pembangun boleh mencipta komponen perisian yang kondusif pelbagai jenis ujian, termasuk ujian unit, penyepaduan, kefungsian, beban dan prestasi. Pendekatan holistik untuk ujian ini membolehkan pengesanan kesalahan dan kesilapan pada awal kitaran pembangunan, mengurangkan kemungkinan masalah hiliran.

DFT yang berkesan mempertimbangkan keseluruhan spektrum ujian, memastikan komponen direka bentuk dengan mengambil kira kebolehujian. Pendekatan ini memudahkan pengasingan kesalahan cepat, mengurangkan masa dan sumber diperlukan untuk mengenal pasti dan membetulkan kesilapan pembuatan dan kegagalan komponen.

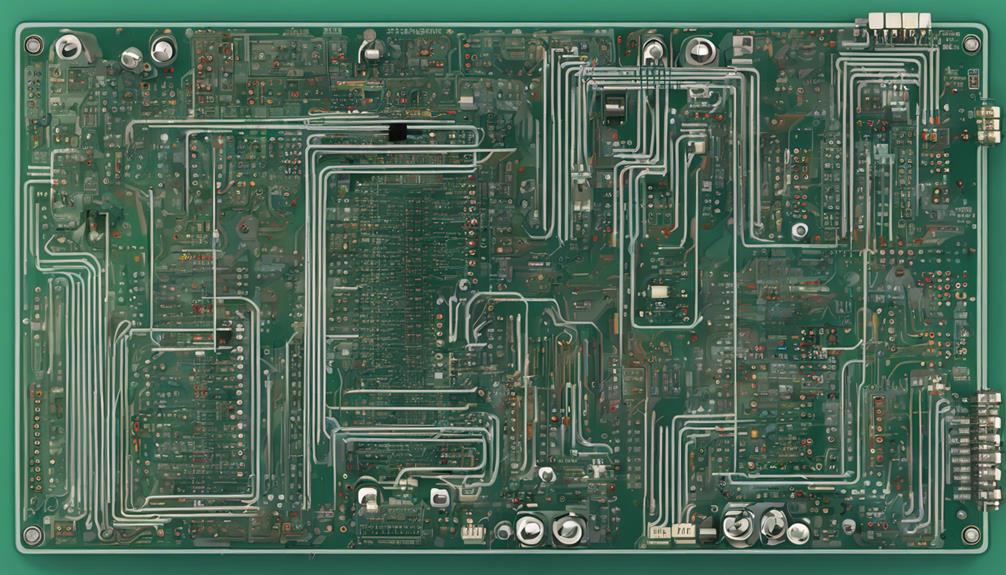

Susun Atur PCB untuk Kebolehujian Maksimum

Untuk kebolehujian yang menyeluruh, reka letak papan litar bercetak (PCB) hendaklah direka bentuk dengan titik ujian yang disengajakan dan ciri kebolehcapaian yang memudahkan ujian yang cekap dan diagnosis kesalahan. Susun atur PCB yang direka dengan baik boleh mengurangkan kerumitan dan kos ujian.

Untuk mencapai kebolehujian maksimum, garis panduan berikut harus diikuti:

- Liputan ujian menyeluruh: Reka bentuk susun atur PCB dengan mata ICT pada setiap jaring untuk menjamin liputan ujian menyeluruh.

- Pembersihan daripada komponen: Kekalkan kelegaan minimum 50 mil antara titik ujian dan komponen serta pad.

- Kelegaan tepi: Kekalkan jarak 100 mil antara titik ujian dan tepi papan untuk kebolehaksesan.

- Penempatan titik siasatan: Letakkan titik probe secara strategik untuk ujian manual bagi memudahkan akses mudah oleh juruteknik.

Melaksanakan Mata Ujian Secara Strategik

Titik ujian yang diposisikan secara strategik adalah penting untuk menjamin liputan menyeluruh sambungan kritikal pada PCB, memudahkan ujian yang cekap dan diagnosis kesalahan.

Dengan memasukkan mata ujian ke dalam reka bentuk PCB, jurutera boleh memastikan bahawa ujian unit adalah terperinci, dan kesalahan boleh dikenal pasti dan diasingkan dengan cepat.

Untuk mencapai kebolehujian yang ideal, mata ujian hendaklah diletakkan secara strategik dengan mengambil kira kebolehcapaian, pelepasan dan keperluan integriti isyarat. Jarak yang betul antara titik ujian juga penting untuk mengelakkan litar pintas dan memastikan prosedur ujian yang boleh dipercayai.

Selain itu, titik ujian yang diletakkan berhampiran komponen utama membolehkan cekap pengasingan kesalahan dan penyelesaian masalah semasa ujian.

Penempatan titik ujian yang berkesan bukan sahaja memudahkan proses ujian tetapi juga meminimumkan kerumitan lekapan ujian, mengurangkan kos ujian dan masa.

Reka Bentuk Boleh Diuji untuk Kebolehkilangan

Mengoptimumkan susun atur PCB untuk kebolehkilangan memerlukan reka bentuk yang boleh diuji yang menyepadukan mata ICT pada setiap jaringan reka bentuk untuk menjamin liputan ujian yang menyeluruh dan memudahkan aliran kerja pengeluaran yang cekap. Pendekatan ini membolehkan pengeluar kontrak (CM) menjalankan ujian ICT, memastikan kedua-dua belah PCB diuji secara serentak.

Untuk menjamin kebolehujian yang berkesan, garis panduan berikut harus dipatuhi:

- Titik ujian yang boleh diakses: Menjamin pelepasan 50 juta kepada komponen dan pad untuk kebolehcapaian yang mudah.

- Penempatan strategik: Letakkan mata ujian berdasarkan garis panduan DFT untuk mengurangkan kerumitan lekapan dan potensi kos tambahan.

- Ujian manual yang mudah: Letakkan titik probe untuk akses mudah oleh juruteknik.

- Ujian yang diselaraskan: Bekerjasama dengan CM untuk menyelaraskan ujian ICT untuk aliran kerja pengeluaran yang cekap.

Penggunaan Vektor Ujian yang Cekap

Dalam domain reka bentuk untuk kebolehujian, penggunaan vektor ujian yang cekap adalah penting untuk menjamin ujian menyeluruh kefungsian litar.

Untuk mencapai matlamat ini, adalah penting untuk menggunakan kaedah penjanaan vektor yang berkesan yang boleh menghasilkan set vektor ujian yang pelbagai, dengan itu mengoptimumkan liputan ujian.

Kaedah Penjanaan Vektor

Selalunya, kecekapan reka bentuk untuk kebolehujian sangat bergantung pada penjanaan vektor ujian yang berkesan, yang penting untuk mengesahkan kelakuan reka bentuk dalam ujian (DUT).

Dalam ujian unit, vektor ujian ialah corak input yang digunakan untuk mengesahkan kelakuan DUT, dan penjanaan cekapnya adalah penting untuk liputan menyeluruh kefungsian DUT.

Untuk menjamin ujian yang cekap, pelbagai algoritma boleh digunakan untuk penjanaan vektor ujian. Ini termasuk:

- Penjanaan vektor ujian pseudo-rawak, yang mengimbangi rawak dan kebolehulangan untuk ujian yang berkesan.

- Penjanaan vektor ujian menyeluruh, yang melibatkan penjanaan semua corak input yang mungkin.

- Penjanaan vektor pintar, yang mengoptimumkan liputan ujian sambil meminimumkan masa dan sumber ujian.

- Penjanaan vektor ujian berasaskan kekangan, yang menjana vektor ujian berdasarkan kekangan khusus dan garis panduan kebolehujian.

Mengoptimumkan Liputan Ujian

Mengoptimumkan Liputan Ujian

Pemilihan titik ujian yang strategik adalah penting untuk memaksimumkan liputan kerosakan dalam ujian PCB, kerana ia membolehkan penggunaan vektor ujian yang cekap untuk menyasarkan kawasan khusus reka bentuk yang sedang diuji. Pendekatan ini menjamin bahawa kemungkinan kecacatan dikenal pasti dan ditangani, mengurangkan risiko PCB yang rosak. Peruntukan vektor ujian yang betul boleh mengurangkan masa ujian dengan ketara sambil memastikan liputan menyeluruh.

| Teknik Pengoptimuman | Faedah |

|---|---|

| Ujian Imbasan Sempadan | Kecekapan vektor ujian dipertingkatkan dengan mengakses nod dalaman |

| Uji Penggunaan Semula Vektor | Mengurangkan masa ujian dan mempertingkatkan peruntukan sumber |

| Ujian Berorientasikan Kecacatan | Ujian disasarkan bagi kawasan berkemungkinan tinggi kerosakan |

| Ujian berasaskan ATPG | Perlindungan kerosakan yang cekap dengan penjanaan corak ujian automatik |

| Ujian Hibrid | Menggabungkan teknik yang berbeza untuk liputan menyeluruh |

Memudahkan Reka Bentuk Litar Kompleks

Memecahkan litar rumit kepada komponen yang lebih kecil dan lebih mudah diurus adalah langkah penting dalam memudahkan reka bentuk litar yang kompleks. Ini membolehkan pereka bentuk menangani setiap modul secara individu, meningkatkan kebolehujian keseluruhan. Pendekatan ini membolehkan pereka bentuk menumpukan pada modul tertentu, mengurangkan kerumitan reka bentuk keseluruhan.

Untuk mencapai matlamat ini, pereka boleh menggunakan beberapa strategi:

- Reka bentuk modular: Memecahkan litar kompleks kepada modul boleh guna semula menggalakkan ujian dan penyelenggaraan yang lebih mudah.

- Kurangkan kebergantungan: Meminimumkan kebergantungan antara komponen memudahkan reka bentuk dan menambah baik pengasingan kerosakan.

- Dokumentasi yang jelas: Menyediakan dokumentasi ringkas dan jelas bagi reka bentuk litar kompleks memudahkan pemahaman dan ujian kefungsian reka bentuk.

- Corak reka bentuk: Melaksanakan corak reka bentuk, seperti corak Pemerhati, boleh memudahkan interaksi litar yang kompleks dan meningkatkan kebolehujian.

Penghalaan Isyarat Berkesan untuk Ujian

Apabila mereka bentuk untuk kebolehujian, berkesan penghalaan isyarat adalah penting untuk menjamin ukuran yang tepat, dan strategi penghalaan isyarat yang dirancang dengan baik boleh mengurangkan ralat dan mempertingkatkan kecekapan ujian.

Untuk mencapai matlamat ini, adalah penting untuk meminimumkan panjang isyarat untuk memastikan ukuran yang tepat. Selain itu, pasangan isyarat pembezaan harus disalurkan bersama untuk dikekalkan integriti isyarat semasa ujian. Ini menghalang kemerosotan isyarat dan memastikan keputusan ujian yang boleh dipercayai.

Di samping itu, adalah penting untuk mengelakkan isyarat penghalaan berhampiran komponen bising untuk mengelakkan gangguan semasa ujian. Jejak impedans terkawal hendaklah digunakan untuk mengekalkan integriti dan ketepatan isyarat semasa ujian. Ini memastikan bahawa isyarat ujian tidak diherotkan, memberikan hasil ujian yang boleh dipercayai.

Melaksanakan titik ujian di lokasi strategik juga penting untuk akses mudah dan proses ujian yang cekap. Dengan menggabungkan ini pertimbangan reka bentuk, pereka bentuk boleh memastikan bahawa strategi penghalaan isyarat mereka dioptimumkan untuk kebolehujian, menghasilkan ujian yang cekap dan tepat.

Penghalaan isyarat yang berkesan ialah aspek kritikal reka bentuk untuk kebolehujian, dan dengan mengikuti amalan terbaik ini, pereka bentuk boleh memastikan ujian yang boleh dipercayai dan cekap.

Merekabentuk untuk Ujian Dalam Litar

Apabila mereka bentuk papan litar bercetak (PCB) untuk ujian dalam litar (ICT), pertimbangan yang teliti mesti diberikan kepada penempatan komponen, pengenalpastian mata ujian, dan penghalaan isyarat untuk menjamin ujian yang cekap dan berkesan. Dengan mengoptimumkan faktor-faktor ini, pereka bentuk boleh memudahkan liputan ICT dan pengasingan kerosakan pantas, akhirnya mengurangkan kos pengeluaran dan meningkatkan kualiti produk.

Dalam bahagian berikut, kami akan mengkaji perkara utama penempatan komponen yang boleh diakses, pengenalpastian titik ujian, dan pertimbangan penghalaan isyarat yang membolehkan ICT berjaya.

Penempatan Komponen Boleh Diakses

Peletakan komponen mudah diakses yang betul adalah penting dalam mereka bentuk ujian dalam litar, kerana ia membolehkan penempatan titik ujian yang cekap dan menjamin liputan ujian menyeluruh. Ini penting untuk ujian unit, kerana ia memastikan kod reka bentuk boleh diuji secara menyeluruh.

Dalam ujian ICT, titik ujian diletakkan secara strategik untuk memudahkan akses mudah untuk peralatan ujian dan juruteknik, mengurangkan kerumitan ujian.

Untuk mencapai penempatan komponen yang ideal, pereka bentuk harus mempertimbangkan garis panduan berikut:

- Keperluan pelepasan: Pastikan kelegaan 50 mil ke komponen dan kelegaan 100 mil ke tepi papan.

- Penempatan titik ujian: Cari titik ujian secara strategik pada susun atur PCB, mempertimbangkan keperluan pelepasan untuk ujian yang cekap.

- Kebolehcapaian komponen: Pastikan komponen boleh diakses untuk tujuan ujian, mengurangkan kerumitan ujian.

- Liputan ujian yang cekap: Jaminan liputan ujian menyeluruh dengan meletakkan titik ujian dengan cara yang membolehkan ujian menyeluruh.

Pengenalpastian Titik Ujian

Dalam mengejar ujian litar yang cekap, pengenalan titik ujian memainkan peranan penting dalam reka bentuk PCB, kerana ia membolehkan penempatan strategik mata khusus pada papan untuk ICT. Penempatan yang disengajakan ini mata ujian ICT memastikan bahawa ia mudah diakses, dengan kelegaan yang mencukupi daripada komponen dan tepi papan, membolehkan ujian yang cekap semasa pengeluaran.

Jarak yang betul antara titik ujian juga penting, kerana ia memastikan ujian yang tepat dan cekap. Titik ujian ini memudahkan penyambungan lekapan ICT, membolehkan proses ujian automatik.

Selain itu, titik ujian yang diletakkan dengan baik dan berlabel membolehkan cepat pengasingan sesar dan penyahpepijatan semasa ICT, memudahkan pengenalpastian dan pembetulan isu. Pengenalpastian titik ujian yang berkesan dalam reka bentuk PCB adalah penting untuk ujian dalam litar yang cekap, menyelaraskan proses ujian dan mengurangkan masa pengeluaran.

Pertimbangan Penghalaan Isyarat

Pertimbangan penghalaan isyarat memainkan peranan penting dalam mereka bentuk ujian dalam litar, kerana ia memberi kesan secara langsung kepada ketepatan dan kebolehpercayaan keputusan ujian. Penghalaan isyarat yang betul adalah penting untuk memastikan ujian PCB yang cekap. Dalam ICT, panjang laluan isyarat harus diminimumkan, dan penghalaan impedans terkawal harus digunakan untuk mengelakkan kemerosotan isyarat.

Untuk mencapai ujian yang boleh dipercayai, pertimbangan penghalaan isyarat berikut harus diambil kira:

- Minimumkan silang: Elakkan isyarat silang antara satu sama lain untuk mengelakkan gangguan elektromagnet dan degradasi isyarat.

- Elakkan selekoh tajam: Gunakan laluan licin dan melengkung untuk mengelakkan pantulan isyarat dan sinaran.

- Hadkan vias: Minimumkan penggunaan vias untuk mengelakkan kehilangan isyarat dan kemerosotan.

- Penempatan titik ujian strategik: Letakkan mata ujian secara strategik untuk memudahkan akses mudah untuk probe ujian, memastikan ujian yang cekap dan boleh dipercayai.

Meningkatkan Liputan dan Kualiti Ujian

Strategi ujian yang berkesan, seperti menggabungkan mata ICT pada setiap jaring reka bentuk, adalah penting untuk menjamin liputan ujian menyeluruh dan kualiti dalam pembuatan PCB. Pendekatan ini membolehkan ujian yang meluas, mengurangkan kemungkinan ralat pembuatan dan kegagalan komponen tidak dapat dikesan.

Dengan memasukkan mata ujian dengan kelegaan yang mencukupi daripada komponen dan kelebihan papan, juruteknik boleh menjalankan dengan cekap ujian unit dan mengenal pasti isu dengan segera. Selain itu, ICT boleh dijalankan serentak di kedua-dua belah lembaga dengan penyelarasan daripada pengilang kontrak, memperkemas proses ujian.

Selain itu, mempunyai titik siasatan yang mudah diakses untuk ujian manual memudahkan prosedur ujian, mengurangkan risiko kesilapan manusia. Liputan ujian kritikal dan jaminan kualiti adalah penting dalam mengenal pasti ralat pembuatan dan kegagalan komponen dengan segera, memastikan itu sahaja PCB berkualiti tinggi dikeluarkan ke pasaran.

Mengoptimumkan Reka Bentuk PCB untuk Ujian

Apabila mengoptimumkan reka bentuk PCB untuk ujian, adalah penting untuk mengambil kira penempatan mata ujian, memastikan bahawa ia mudah diakses untuk ujian yang cekap.

Peletakan mata ujian yang betul memudahkan menyeluruh liputan ujian, mengurangkan masa ujian dan meningkatkan kualiti ujian.

Reka bentuk untuk Kebolehcapaian

Susun atur PCB yang direka dengan baik yang menggabungkan titik ujian yang boleh diakses membolehkan proses ujian yang cekap, mengurangkan masa dan kos yang berkaitan dengan mengenal pasti dan membetulkan kecacatan. Reka bentuk untuk kebolehaksesan ialah aspek kritikal untuk mengoptimumkan reka bentuk PCB untuk ujian, kerana ia memudahkan proses ujian dan memastikan liputan kerosakan yang menyeluruh.

Untuk mencapai kebolehaksesan yang ideal, pereka bentuk harus mempertimbangkan faktor utama berikut:

- Pembersihan dari komponen dan tepi papan: Pastikan titik ujian mempunyai kelegaan yang mencukupi untuk membolehkan akses mudah untuk probe ujian.

- Mata ICT pada setiap jaring reka bentuk: Menggabungkan mata ICT pada setiap jaringan reka bentuk untuk membolehkan liputan ujian menyeluruh semasa pembuatan.

- Kerjasama dengan pengeluar kontrak: Bekerjasama dengan pengeluar kontrak untuk menentukan metodologi ujian dan pengubahsuaian lekapan yang paling berkesan untuk perlindungan kerosakan yang dipertingkatkan.

- Ujian ICT untuk maklum balas segera: Gunakan ujian ICT untuk menerima maklum balas segera tentang ralat pembuatan, kegagalan komponen, dan keseluruhan fungsi PCB, membolehkan pelarasan pantas.

Penempatan Mata Ujian

Meletakkan titik ujian secara strategik pada PCB adalah penting untuk liputan maksimum semasa ujian ICT, kerana ia membolehkan cekap pengesanan kesalahan dan pengasingan semasa pembuatan. Berkesan penempatan titik ujian adalah penting untuk mengoptimumkan reka bentuk PCB untuk kebolehujian. Dengan mengikut Garis panduan DFM, pereka bentuk boleh menentukan lokasi yang sesuai untuk titik ujian pada PCB, memastikan liputan yang ideal dan memudahkan pengesanan kerosakan.

Pelepasan yang betul dari komponen dan tepi papan juga penting untuk memudahkan proses ujian. Titik ujian yang diletakkan dengan baik membolehkan ujian yang cepat dan tepat, yang membawa kepada kualiti produk keseluruhan yang lebih baik. Keperluan ujian ICT harus dipertimbangkan semasa fasa reka bentuk untuk memastikan titik ujian diletakkan secara strategik untuk liputan maksimum.

Soalan Lazim

Apakah Prinsip Reka Bentuk untuk Kebolehujian?

Prinsip reka bentuk untuk kebolehujian berkisar pada pembuatan kod iaitu modular, berganding longgar dan mudah untuk diuji. Ini dicapai dengan mematuhi prinsip seperti Tanggungjawab Tunggal, Terbuka/Tertutup, Penggantian Liskov, Pengasingan Antara Muka dan Penyongsangan Ketergantungan.

Selain itu, pembangunan berasaskan ujian, pemfaktoran semula, dan meminimumkan kebergantungan adalah penting untuk mencipta kod yang boleh diuji. Dengan mengikut prinsip ini, pembangun boleh menulis kod yang boleh diselenggara, berskala dan mudah diuji, menghasilkan kualiti kod yang lebih baik dan mengurangkan hutang teknikal.

Apakah Teknik DFT?

Walaupun reka bentuk PCB tradisional memberi tumpuan kepada estetika dan kefungsian, anjakan paradigma diperlukan untuk mengutamakan kebolehujian.

Teknik DFT ialah pendekatan reka bentuk sengaja yang menyepadukan pertimbangan ujian ke dalam susun atur PCB. Teknik ini termasuk meletakkan secara strategik mata ujian, menggunakan teknik imbasan sempadan, dan melaksanakan ujian kendiri terbina dalam (BIST) keupayaan.

Apakah Garis Panduan PCB dalam Pengujian?

Garis panduan PCB dalam menguji menggariskan keperluan khusus untuk penempatan titik ujian dan kelegaan pada susun atur papan litar bercetak. Garis panduan ini menjamin pengasingan kesalahan yang cekap dan ujian semasa pembuatan PCB, memperkemas proses ujian dan menambah baik pengesanan kesalahan.

Mengapa DFT Diperlukan?

Reka Bentuk untuk Kebolehujian (DFT) adalah aspek penting dalam reka bentuk PCB. Ia membolehkan cekap pengesanan kesalahan dan pengasingan semasa pembuatan, mengurangkan kos pengeluaran dan masa ke pasaran. Dengan menggabungkan prinsip DFT, pengeluar boleh menjamin produk berkualiti tinggi, meminimumkan kecacatan dan menyelaraskan proses ujian.

Pelaksanaan DFT yang berkesan memudahkan pengenalpastian pantas dan penyelesaian kerosakan. Ini akhirnya membawa kepada peningkatan kebolehpercayaan produk dan kepuasan pelanggan.