プリント基板(PCB)設計における電磁干渉(EMI)を低減するには、3つの重要な設計のヒントを考慮する必要があります。まず、最適化します。 PCBレイヤースタックアップ EMI放出を最小限に抑え、 効果的な遮蔽 インピーダンスを制御します。次に、信号放射を最小限に抑えるために、 差動信号技術, 適切な接地、シールド材。最後に、電源とグランドを効率的に配線し、電源とグランドのトレースを分離しながら、 信号整合性 干渉を低減します。これらの設計上の考慮事項の複雑さを理解することで、設計者は EMI を効果的に最小限に抑え、信頼性の高い PCB パフォーマンスを保証し、EMI 低減戦略のニュアンスを明らかにすることができます。

重要なポイント

- 信号層をグランドプレーンに隣接させて配置し、信号パスとリターンパスのバランスをとることで、PCB 層のスタックアップを最適化し、EMI 放出を最小限に抑えます。

- コモンモードノイズと信号放射を減らすには、差動信号技術と、ソリッドグランドプレーンなどの適切な接地方法を採用します。

- 電源トレースとグランド トレースを分離し、低インピーダンス パスを作成し、電圧降下を最小限に抑えることで、電源信号とグランド信号を効率的にルーティングします。

- シールド材と EMI フィルターを使用して電磁信号を封じ込めて抑制し、放射と干渉を防止します。

- 電源とグランドの接続を慎重に配置するなど、ループ領域を最小限に抑えて放射を減らす信号ルーティング戦略を実装します。

PCBレイヤースタックアップの最適化

よく計画されたPCB レイヤースタックアップ 効果的なシールドを可能にするため、電磁干渉(EMI)放出を最小限に抑えるために不可欠です。 制御インピーダンス、効率的 信号ルーティング.

高性能 PCB では、適切に設計されたレイヤー スタックアップが EMI の低減に不可欠です。これは、信号レイヤーをグランド プレーンに隣接して配置することで実現され、効果的なシールドが提供され、EMI の放出が最小限に抑えられます。

さらに、レイヤースタックアップで電源プレーンとグランドプレーンを互いに近づけて配置すると、 ループエリア、EMI放出をさらに最小限に抑えます。信号経路を考慮したバランスの取れたスタックアップと 戻りパス EMI の問題を軽減する上でも重要です。

PCBレイヤースタックを最適化することで、設計者はインピーダンスの制御、効率的な信号ルーティング、EMI干渉の最小化を実現できます。これは、次のような高性能PCBで特に重要です。 信号整合性 最も重要です。

信号放射を最小限に抑える

雇用することで 差動信号技術, 信号を適切に接地する、そして活用 遮蔽材、PCB設計者は最小限に抑えることができます 信号放射、それによって EMI放出 そして確実に 信号整合性 で 高性能アプリケーション.

差動信号技術は、信号放射の重要な要因であるコモンモード ノイズの低減に効果的です。また、ソリッド グラウンド プレーンの使用などの適切な接地技術も、信号放射の低減に重要な役割を果たします。

銅箔や導電性コーティングなどのシールド材は、電磁信号を封じ込め、外部への放射を防ぎます。さらに、ループ領域を最小限に抑え、放射の可能性を減らす信号ルーティング戦略も重要です。

さらに、EMI フィルターとフェライト ビーズを組み込むことで、高周波ノイズを抑制し、信号放射を防ぐことができます。これらの設計戦略を実装することで、PCB 設計者は信号放射を効果的に最小限に抑え、要求の厳しいアプリケーションで信頼性の高い高性能な動作を確保できます。

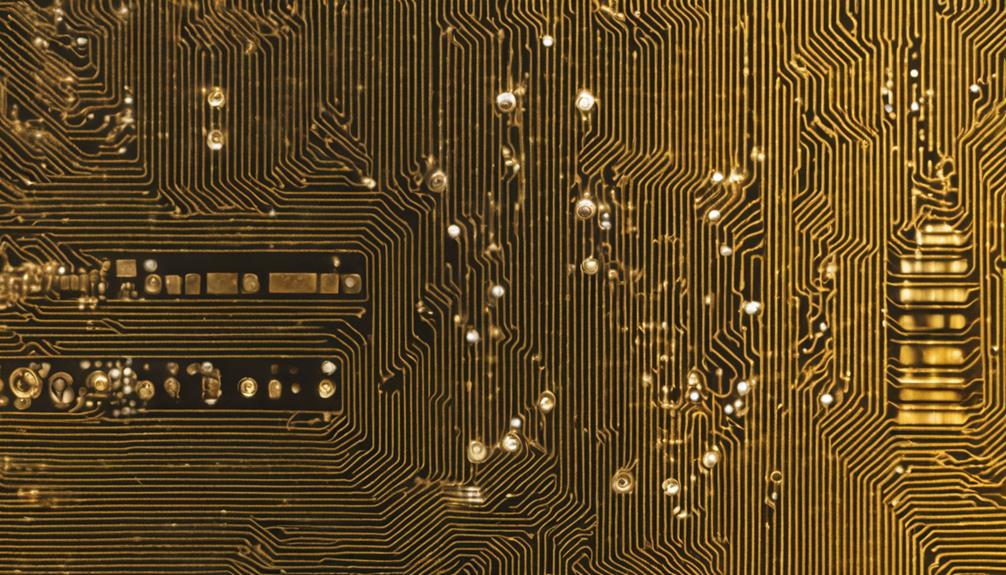

電源と接地を効率的に配線する

電源信号とグランド信号の効率的なルーティングは、ループ領域を減らし、不要な電磁放射を防ぐため、EMI 放出を最小限に抑える上で重要です。これは、高性能アプリケーションで信頼性の高い動作を保証するために不可欠です。

効率的なルーティングを実現するには、次の主要な戦略を検討してください。

- 電源とグランドのトレースを分離する 信号の整合性を維持し、干渉を低減します。

- 適切な配電網を設計する 安定した電圧レベルを保証し、ノイズを低減します。

- しっかりとしたグランドプレーンと電源プレーンを活用する 電源信号とグランド信号用の低インピーダンス パスを作成します。

- 電源とアースの接続を慎重に行う 電圧降下を減らし、EMI の問題を最小限に抑えます。

よくある質問

エミを抑えるテクニックとは?

電子設計の静かな妨害者として、 エミ 影に潜み、最も綿密に作られた回路さえも破壊しようと待ち構えています。

では、EMIを抑制する技術は何でしょうか?効果的な戦略としては、適切な 接地, シールド、およびスイッチングノイズを除去するためのデカップリングコンデンサ。

さらに、分離された電源プレーンとグランドプレーン、慎重な信号ルーティング、低インピーダンスの電力分配ネットワークにより、電磁干渉を最小限に抑えることができます。

PCB 設計で EMI を削減する方法は?

PCB設計におけるEMIの低減には、多面的なアプローチが不可欠です。適切な 接地とシールド技術 戦略的に配置することが重要です デカップリングコンデンサ 電源プレーンとグランドプレーンを分離することも重要なステップです。

さらに、注意深い 信号ルーティング 信号層をグランドプレーンに隣接して配置すると、EMI を大幅に最小限に抑えることができます。これらの設計上の考慮事項を組み込むことで、PCB 設計者は EMI を効果的に軽減し、電磁両立性を保証することができます。

EMI フィルターの使用以外に、EMC EMI 設計に必要なその他の考慮事項は何ですか?

使用を超えて EMIフィルター、効果的なその他の重要な考慮事項 EMC EMI設計 堅牢な実装を含む 接地技術、賢明な信号ルーティング、および慎重なコンポーネント配置。

さらに、デジタル信号とアナログ信号を分離し、低インピーダンスの電力分配ネットワークを活用し、デカップリング コンデンサを組み込むことも不可欠です。

さらに、 コンプライアンステスト EMI の低減を保証し、電磁干渉を軽減するには、CISPR や FCC 規制などの業界標準に準拠することが不可欠です。

EMI と EMC を回避するにはどうすればよいでしょうか?

EMIとEMCの問題を回避するには、設計者は多面的なアプローチを採用する必要があります。適切な 接地技術, 敏感な部品のシールド、デジタル信号とアナログ信号を分離することが不可欠です。効果的なシールド、EMC規格への準拠、そして慎重な 信号ルーティング も不可欠です。

さらに、デカップリング コンデンサを活用し、業界のベスト プラクティスに従うことで、EMI および EMC の課題を軽減し、信頼性が高く効率的な電子システム設計を実現できます。