テスト容易化設計はプリント基板(PCB)設計の重要な側面であり、効率的なテスト、早期の 障害検出、エラーの特定にかかる時間とリソースを削減します。効果的 テスト容易性を考慮した設計 実装を含む 戦略的にポイントをテストするクリアランスとアクセス性を維持し、最適化する 信号ルーティングまた、テストベクトルの効率的な使用、製造性を考慮した設計、および強化も含まれます。 テスト範囲と品質基本的なベスト プラクティスに従うことで、設計者は徹底したテスト範囲を保証し、テストの複雑さを軽減し、生産を合理化できます。テスト可能性の重要性が高まり続けるにつれて、これらの原則を理解することが PCB の設計と製造を成功させる上でますます重要になります。

重要なポイント

- すべての設計ネットに ICT ポイントを組み込み、アクセシビリティのためにテスト ポイントを戦略的に配置することで、徹底したテスト カバレッジを確保します。

- コンポーネントからのクリアランス、エッジのクリアランス、および戦略的なプローブ ポイントの配置を維持する PCB レイアウト戦略を実装して、テストの複雑さを軽減します。

- すべての設計ネットに ICT ポイントを配置し、簡単にクリアランスできるアクセス可能なテスト ポイントを確保し、DFT ガイドラインに従うことで、製造性を考慮した設計を実現します。

- 疑似ランダム、網羅的、インテリジェント、制約ベースのアプローチなどの方法で生成された効率的なテスト ベクトルを使用して、障害カバレッジを最大化します。

- ICT ポイントを組み込み、広範なテストを実施し、ユニット テストを実装して製造エラーやコンポーネント障害を迅速に特定することで、テストの範囲と品質を強化します。

テスト容易性設計の基礎

テスト容易性設計(DFT)は、ソフトウェアおよびハードウェア開発において、テスト容易性の作成に重点を置く重要な概念です。 テストを容易にするコンポーネントこれにより、最終製品の品質と信頼性が向上します。

DFTの原理を取り入れることで、開発者は次のようなソフトウェアコンポーネントを作成することができます。 さまざまなテストの種類ユニットテスト、統合テスト、機能テスト、負荷テスト、パフォーマンステストなど、包括的なテストアプローチにより、 障害やエラーの検出 開発サイクルの早い段階で、下流で問題が発生する可能性を減らします。

効果的なDFTはテスト範囲全体を考慮し、コンポーネントがテスト可能性を考慮して設計されることを保証します。このアプローチは、 迅速な障害分離, 時間とリソースの削減 特定し、修正する必要がある 製造上の誤りと部品の故障.

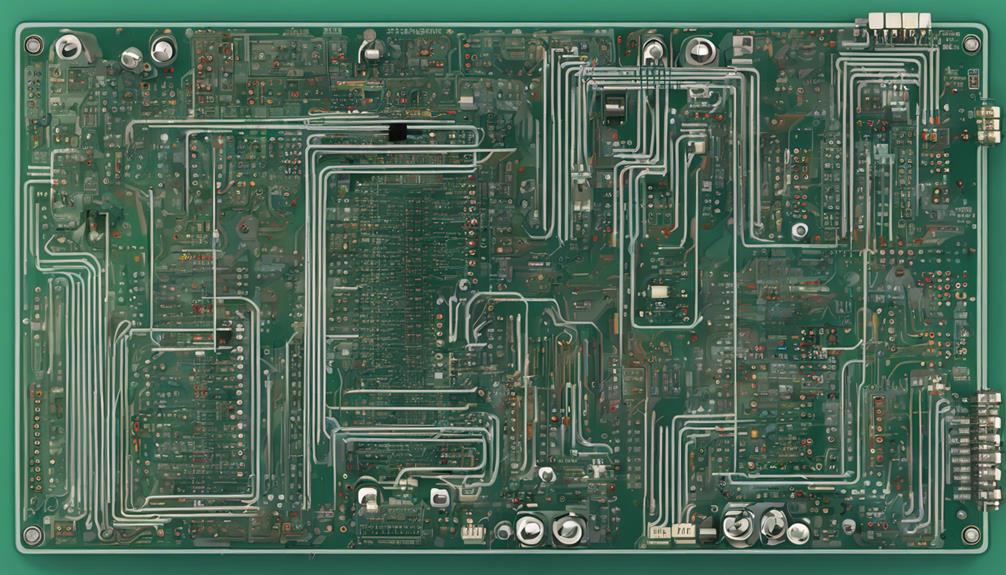

テスト可能性を最大限に高める PCB レイアウト

徹底したテスト可能性を実現するには、プリント回路基板 (PCB) レイアウトを、効率的なテストと障害診断を容易にする意図的なテスト ポイントとアクセシビリティ機能を使用して設計する必要があります。適切に設計された PCB レイアウトにより、テストの複雑さとコストを大幅に削減できます。

最大限のテスト可能性を実現するには、次のガイドラインに従う必要があります。

- 徹底したテスト範囲: 徹底したテスト範囲を保証するために、各ネットに ICT ポイントを備えた PCB レイアウトを設計します。

- コンポーネントからのクリアランステスト ポイントとコンポーネントおよびパッドの間の最小クリアランスは 50 ミルに維持します。

- エッジクリアランスアクセス性を確保するために、テスト ポイントとボードの端の間に 100 ミルのクリアランスを維持します。

- プローブポイントの配置: 技術者が簡単にアクセスできるように、手動テスト用のプローブ ポイントを戦略的に配置します。

テストポイントを戦略的に実装する

戦略的に配置されたテストポイントは、PCB上の重要な接続部を徹底的にカバーするために不可欠であり、 効率的なテストと障害診断.

テスト ポイントを PCB 設計に組み込むことで、エンジニアはユニット テストを詳細に実行し、障害を迅速に特定して分離できるようになります。

理想的なテスト可能性を実現するには、アクセス性、クリアランス、および 信号整合性要件. テストポイント間の適切な間隔 ショートを防ぎ、 信頼性の高いテスト手順.

さらに、主要コンポーネントの近くにテストポイントを配置することで、効率的な 障害の分離とトラブルシューティング テスト中。

テストポイントを効果的に配置することで、テストプロセスが簡素化されるだけでなく、テストフィクスチャの複雑さが最小限に抑えられ、 テストのコストと時間.

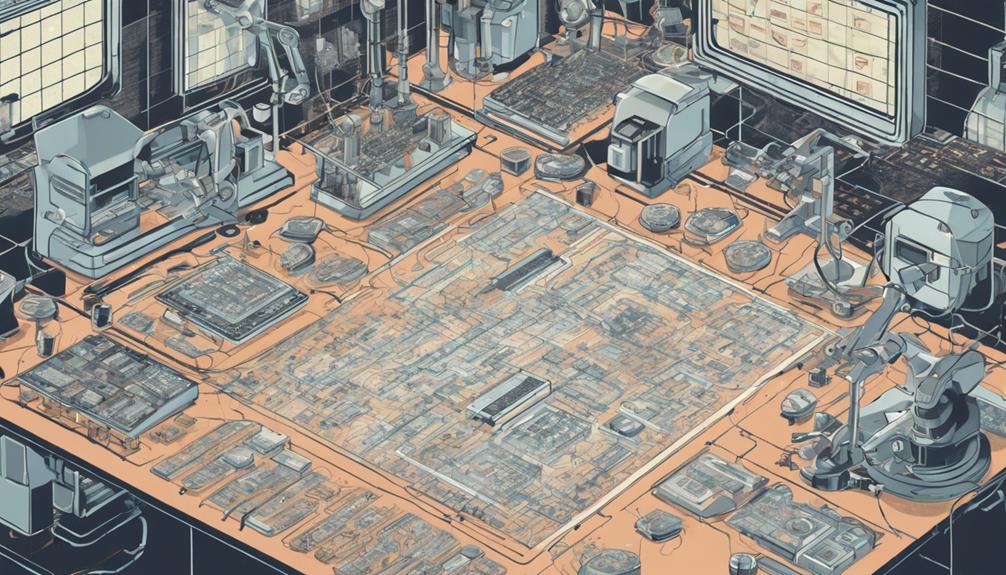

製造性を考慮したテスト可能な設計

製造性を考慮して PCB レイアウトを最適化するには、すべての設計ネットに ICT ポイントを統合し、テスト範囲を徹底的に保証して効率的な製造ワークフローを促進するテスト可能な設計が必要です。このアプローチにより、契約製造業者 (CM) は ICT テストを実施し、PCB の両面を同時にテストできるようになります。

効果的なテスト可能性を保証するには、次のガイドラインに従う必要があります。

- アクセス可能なテストポイント: 簡単にアクセスできるように、コンポーネントとパッドの間の 50 ミルのクリアランスを保証します。

- 戦略的な配置: DFT ガイドラインに基づいてテスト ポイントを配置し、治具の複雑さと潜在的な追加コストを削減します。

- 簡単な手動テスト: 技術者が簡単にアクセスできる場所にプローブ ポイントを配置します。

- 協調テスト: CM と協力して、効率的な生産ワークフローのための ICT テストを調整します。

テストベクトルの効率的な使用

の領域では テスト容易性を考慮した設計回路の機能性を徹底的にテストするには、テスト ベクトルを効率的に使用することが重要です。

これを達成するには、多様なテストベクトルセットを生成できる効果的なベクトル生成方法を採用することが不可欠であり、それによって最適化される。 テスト範囲.

ベクトル生成方法

多くの場合、テスト容易化設計の効率は、テスト対象設計 (DUT) の動作を検証するために不可欠なテスト ベクトルの効率的な生成に大きく依存します。

ユニット テストでは、テスト ベクトルは DUT の動作を検証するために使用される入力パターンであり、その効率的な生成は DUT 機能の徹底的なカバレッジにとって重要です。

効率的なテストを保証するために、テスト ベクトル生成にはさまざまなアルゴリズムを採用できます。これには次のものが含まれます。

- 疑似ランダムテストベクトル生成ランダム性と再現性のバランスをとることで、効果的なテストを実現します。

- 徹底的なテストベクトル生成これには、すべての可能な入力パターンの生成が含まれます。

- インテリジェントなベクトル生成これにより、テスト時間とリソースを最小限に抑えながらテスト範囲が最適化されます。

- 制約ベースのテストベクトル生成特定の制約とテスト可能性ガイドラインに基づいてテスト ベクトルを生成します。

テスト範囲の最適化

テスト範囲の最適化

テスト ポイントを戦略的に選択することは、PCB テストにおける障害カバレッジを最大化するために不可欠です。これにより、テスト ベクトルを効率的に使用して、テスト対象の設計の特定の領域をターゲットにすることができます。このアプローチにより、潜在的な欠陥が確実に特定され、対処されるため、PCB の障害リスクが軽減されます。テスト ベクトルを適切に割り当てると、徹底したカバレッジを確保しながら、テスト時間を大幅に短縮できます。

| 最適化手法 | 利点 |

|---|---|

| 境界スキャンテスト | 内部ノードへのアクセスによるテストベクトル効率の向上 |

| テストベクトルの再利用 | テスト時間の短縮とリソース割り当ての改善 |

| 欠陥指向テスト | 故障確率の高い領域をターゲットにしたテスト |

| ATPGベースのテスト | 自動テストパターン生成による効率的な障害検出 |

| ハイブリッドテスト | さまざまな技術を組み合わせて包括的なカバレッジを実現 |

複雑な回路設計を簡素化

複雑な回路をより小さく、管理しやすいコンポーネントに分割することは、複雑な回路設計を簡素化する上で不可欠なステップです。これにより、設計者は各モジュールを個別に処理できるようになり、全体的なテスト可能性が向上します。このアプローチにより、設計者は特定のモジュールに集中でき、全体的な設計の複雑さが軽減されます。

これを実現するために、設計者はいくつかの戦略を採用できます。

- モジュール設計複雑な回路を再利用可能なモジュールに分解すると、テストとメンテナンスが容易になります。

- 依存関係を減らす: コンポーネント間の依存関係を最小限に抑えることで、設計が簡素化され、障害の分離が向上します。

- 明確なドキュメント: 複雑な回路設計の簡潔で明確なドキュメントを提供することで、設計の機能の理解とテストが容易になります。

- デザインパターン: Observer パターンなどの設計パターンを実装すると、複雑な回路の相互作用が簡素化され、テスト可能性が向上します。

テストのための効果的な信号ルーティング

テスト可能性を考慮した設計では、効果的な 信号ルーティング 保証するために不可欠である 正確な測定、そしてよく計画された信号ルーティング戦略は、エラーを大幅に削減し、 テスト効率.

これを達成するには、正確な測定を保証するために信号長を最小化することが重要です。さらに、差動信号ペアは、 信号整合性 これにより、テスト中に 信号劣化 そして保証する 信頼できるテスト結果.

さらに、テスト中の干渉を防ぐために、ノイズの多いコンポーネントの近くに信号をルーティングしないようにすることが重要です。 制御されたインピーダンストレース テスト中に信号の整合性と精度を維持するために使用する必要があります。これにより、テスト信号が歪むことがなくなり、信頼性の高いテスト結果が得られます。

戦略的な場所にテストポイントを実装することも、アクセスの容易さと効率的なテストプロセスにとって重要です。これらを組み込むことで、 設計上の考慮事項設計者は、信号ルーティング戦略がテスト容易性のために最適化されていることを確認でき、効率的で正確なテストが可能になります。

効果的な信号ルーティングはテスト容易性設計の重要な側面であり、これらのベスト プラクティスに従うことで、設計者は信頼性が高く効率的なテストを保証できます。

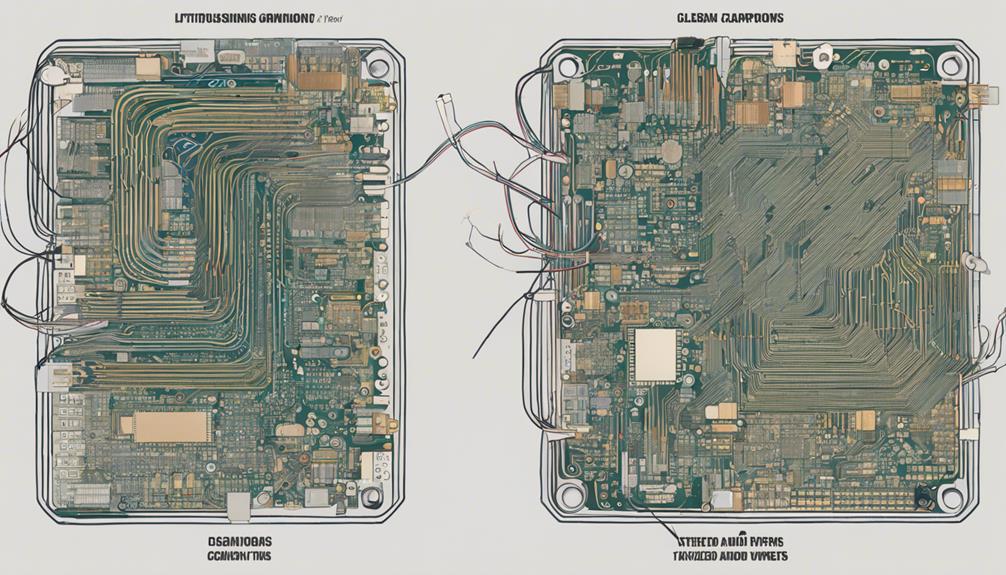

インサーキットテストの設計

インサーキットテスト(ICT)用のプリント基板(PCB)を設計する場合、部品の配置、部品の識別、および部品の実装について慎重に考慮する必要があります。 テストポイント、 そして 信号ルーティング 効率的で効果的なテストを保証します。これらの要素を最適化することで、設計者は ICT カバレッジと迅速な障害分離を促進し、最終的に製造コストを削減し、製品品質を向上させることができます。

以下のセクションでは、 キーポイント アクセス可能なコンポーネントの配置、テスト ポイントの識別、および信号ルーティングの考慮事項により、ICT を成功に導きます。

アクセス可能なコンポーネント配置

アクセス可能な適切なコンポーネント配置は、効率的なテスト ポイント配置を可能にし、徹底したテスト範囲を保証するため、インサーキット テストの設計に不可欠です。これは、設計コードを包括的にテストできることを保証するため、ユニット テストにとって非常に重要です。

ICT テストでは、テスト機器や技術者が簡単にアクセスできるようにテスト ポイントが戦略的に配置され、テストの複雑さが軽減されます。

理想的なコンポーネント配置を実現するために、設計者は次のガイドラインを考慮する必要があります。

- クリアランス要件: コンポーネントまでのクリアランスが 50 ミル、ボードの端までのクリアランスが 100 ミルであることを確認します。

- テストポイントの配置: 効率的なテストのためのクリアランス要件を考慮して、PCB レイアウト上のテスト ポイントを戦略的に配置します。

- コンポーネントのアクセシビリティ: テスト目的でコンポーネントにアクセスできるようにし、テストの複雑さを軽減します。

- 効率的なテスト範囲包括的なテストを可能にする方法でテストポイントを配置することにより、徹底したテスト範囲を保証します。

テストポイントの識別

効率的なインサーキットテストの追求において、 テストポイントの識別 PCB設計において、ICT専用のポイントをボード上に戦略的に配置することを可能にするという重要な役割を果たします。 ICTテストポイント 部品や基板の端から十分なスペースを確保し、簡単にアクセスできるようにします。 効率的なテスト 制作中。

テストポイント間の適切な間隔も、正確で効率的なテストを保証するために重要です。これらのテストポイントは、 ICT設備自動化されたテストプロセスを可能にします。

さらに、適切に配置されラベル付けされたテストポイントにより、 誤った隔離 そして ICT中のデバッグ、問題の特定と修正を容易にします。PCB 設計における効果的なテスト ポイントの特定は、効率的なインサーキット テスト、テスト プロセスの合理化、および製造時間の短縮に不可欠です。

信号ルーティングの考慮事項

信号ルーティングの考慮は、テスト結果の精度と信頼性に直接影響するため、インサーキット テストの設計において重要な役割を果たします。適切な信号ルーティングは、PCB の効率的なテストに不可欠です。ICT では、信号パスの長さを最小限に抑え、制御されたインピーダンス ルーティングを使用して信号の劣化を防ぐ必要があります。

信頼性の高いテストを実現するには、次の信号ルーティングの考慮事項を考慮する必要があります。

- クロスオーバーを最小限に抑える: 電磁干渉や信号劣化を防ぐため、信号が交差しないようにしてください。

- 急カーブを避ける: 信号の反射や放射を防ぐために、滑らかな曲線のルートを使用します。

- ビアの制限: 信号の損失や劣化を防ぐために、ビアの使用を最小限に抑えます。

- 戦略的なテストポイントの配置: テスト ポイントを戦略的に配置してテスト プローブのアクセスを容易にし、効率的で信頼性の高いテストを実現します。

テスト範囲と品質の向上

効果的なテスト戦略、例えば ICTポイントの組み込み 各デザインネット上で、保証するために不可欠です 徹底したテスト範囲 PCB製造における品質の向上。このアプローチにより、 広範囲にわたるテスト製造上の誤りやコンポーネントの故障が検出されない可能性を減らします。

コンポーネントと基板の端から十分な距離を置いたテストポイントを設けることで、技術者は効率的にテストを実施できます。 ユニットテスト 問題を迅速に特定できます。さらに、契約メーカーとの調整により、ICT をボードの両側で同時に実行できるため、テスト プロセスが効率化されます。

さらに、手動テスト用のプローブ ポイントに簡単にアクセスできるため、テスト手順が簡素化され、人為的エラーのリスクが軽減されます。 重要なテスト範囲 品質保証は、製造上の誤りや部品の故障を迅速に特定し、 高品質のPCB 市場に放出されます。

テストのためのPCB設計の最適化

テスト用にPCB設計を最適化する際には、 テストポイント効率的なテストのために簡単にアクセスできるようにします。

適切なテストポイントの配置により、徹底した テスト範囲テスト時間を短縮し、テスト品質を向上させます。

アクセシビリティを考慮したデザイン

アクセス可能なテスト ポイントを組み込んだ適切に設計された PCB レイアウトにより、効率的なテスト プロセスが可能になり、欠陥の特定と修正に関連する時間とコストが削減されます。アクセシビリティを考慮した設計は、テスト プロセスを容易にし、完全な障害カバレッジを保証するため、テスト用に PCB 設計を最適化する上で重要な要素です。

理想的なアクセシビリティを実現するには、設計者は次の重要な要素を考慮する必要があります。

- 部品と基板の端からのクリアランス: テストポイントに十分なクリアランスがあり、テストプローブが簡単にアクセスできることを確認します。

- 各デザインネット上のICTポイント: 各設計ネットに ICT ポイントを組み込み、製造中に徹底したテスト カバレッジを実現します。

- 契約メーカーとの連携: 契約メーカーと協力して、障害範囲の拡大に最も効果的なテスト方法と治具の変更を決定します。

- 即時フィードバックのためのICTテスト: ICT テストを利用して、製造エラー、コンポーネントの障害、および PCB 全体の機能に関するフィードバックを即座に受け取り、迅速な調整を可能にします。

テストポイントの配置

PCB上にテストポイントを戦略的に配置することは、テスト中に最大限のカバレッジを得るために不可欠です。 ICTテスト効率的な 障害検出 製造中の分離と効果的な テストポイントの配置 最適化には重要です PCB設計 テスト可能性のために。 DFMガイドライン設計者は、PCB 上のテスト ポイントの理想的な位置を決定し、理想的なカバレッジを確保して障害検出を容易にすることができます。

コンポーネントとボードの端からの適切なクリアランスも、テスト プロセスを容易にするために不可欠です。テスト ポイントを適切に配置すると、迅速かつ正確なテストが可能になり、製品全体の品質が向上します。テスト ポイントが戦略的に配置され、最大範囲をカバーできるように、設計段階で ICT テスト要件を考慮する必要があります。

よくある質問

テスト容易性設計の原則とは何ですか?

テスト容易性設計の原則は、次のようなコードを作成することを中心に展開されます。 モジュラー、疎結合、テストが容易です。これは、単一責任、オープン/クローズ、リスコフ置換、インターフェース分離、依存性反転などの原則に従うことで実現されます。

さらに、 テスト駆動開発, リファクタリング、 そして 依存関係を最小限に抑える テスト可能なコードを作成するには、これらの原則が不可欠です。これらの原則に従うことで、開発者は保守可能で、スケーラブルで、テストしやすいコードを作成でき、コードの品質が向上し、技術的負債が軽減されます。

DFT 技術とは何ですか?

従来の PCB 設計では美観と機能性に重点が置かれていましたが、テスト可能性を優先するにはパラダイム シフトが必要です。

DFT技術は、PCBレイアウトにテストの考慮を組み込んだ意図的な設計アプローチです。これらの技術には、戦略的に配置することが含まれます。 テストポイント、使用 境界スキャン技術、および実装 内蔵セルフテスト (BIST) 機能。

テストにおける PCB ガイドラインとは何ですか?

PCBのテストガイドラインでは、 テストポイントの配置 プリント基板レイアウトのクリアランスと設計。これらのガイドラインは、PCB製造中の効率的な障害分離とテストを保証し、テストプロセスを合理化し、改善します。 障害検出.

DFT が必要な理由

テスト容易化設計(DFT)はPCB設計の重要な側面です。これにより、効率的な 障害検出 製造中の分離と分離により、生産コストと市場投入までの時間が削減されます。DFTの原則を取り入れることで、メーカーは 高品質の製品欠陥を最小限に抑え、テスト プロセスを合理化します。

効果的な DFT の実装により、障害の迅速な特定と解決が容易になり、最終的には製品の信頼性と顧客満足度が向上します。