La progettazione finalizzata alla testabilità è un aspetto essenziale della progettazione dei circuiti stampati (PCB), poiché garantisce test efficienti fin dalle prime fasi rilevamento dei guastie riduzione dei tempi e delle risorse per l'identificazione degli errori. Efficace progettazione per la testabilità comporta l'implementazione testare i punti strategicamente, mantenendo lo spazio libero e l'accessibilità e ottimizzando instradamento del segnale. Comprende anche l'utilizzo efficiente dei vettori di test, la progettazione per la producibilità e il miglioramento copertura e qualità del test. Seguendo le migliori pratiche essenziali, i progettisti possono garantire una copertura completa dei test, ridurre la complessità dei test e semplificare la produzione. Poiché l'importanza della testabilità continua a crescere, la comprensione di questi principi diventa sempre più importante per una progettazione e una produzione di PCB di successo.

Punti chiave

- Garantire una copertura approfondita dei test incorporando punti ICT su ogni rete di progettazione e posizionando strategicamente i punti di test per l'accessibilità.

- Implementa strategie di layout PCB che mantengano la distanza dai componenti, la distanza dai bordi e il posizionamento strategico dei punti della sonda per ridurre la complessità dei test.

- Progettare per la producibilità posizionando i punti ICT su ogni rete di progettazione, garantendo punti di prova accessibili con facile sgombero e seguendo le linee guida DFT.

- Utilizza vettori di test efficienti generati attraverso metodi come approcci pseudo-casuali, esaustivi, intelligenti e basati su vincoli per massimizzare la copertura dei guasti.

- Migliorare la copertura e la qualità dei test incorporando punti ICT, conducendo test approfonditi e implementando test unitari per identificare tempestivamente errori di produzione e guasti dei componenti.

Fondamenti di progettazione per la testabilità

Design for Testability (DFT) è un concetto essenziale nello sviluppo di software e hardware che enfatizza la creazione di componenti che promuovono test facili, garantendo così una migliore qualità e affidabilità del prodotto finale.

Incorporando i principi DFT, gli sviluppatori possono creare componenti software favorevoli vari tipi di test, inclusi test di unità, integrazione, funzionali, di carico e di prestazioni. Questo approccio olistico ai test consente rilevamento di guasti ed errori all'inizio del ciclo di sviluppo, riducendo la probabilità di problemi a valle.

Un DFT efficace considera l'intero spettro di test, garantendo che i componenti siano progettati tenendo presente la testabilità. Questo approccio facilita rapido isolamento dei guasti, riducendo tempo e risorse necessario identificare e correggere errori di produzione e guasti dei componenti.

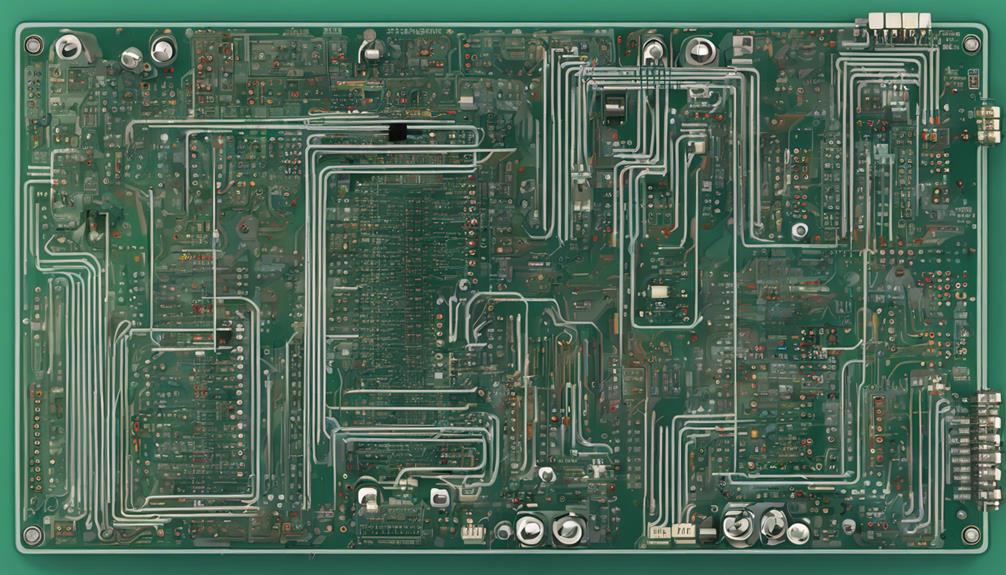

Layout PCB per la massima testabilità

Per una verificabilità approfondita, i layout dei circuiti stampati (PCB) dovrebbero essere progettati con punti di test intenzionali e caratteristiche di accessibilità che facilitino test efficienti e diagnosi dei guasti. Un layout PCB ben progettato può ridurre notevolmente la complessità e i costi dei test.

Per ottenere la massima testabilità, è necessario seguire le seguenti linee guida:

- Copertura di test completa: Progetta layout PCB con punti ICT su ciascuna rete per garantire una copertura completa dei test.

- Distanza dai componenti: Mantenere una distanza minima di 50 mil tra i punti di prova, i componenti e le pastiglie.

- Distanza dai bordi: Mantenere uno spazio di 100 mil tra i punti di prova e il bordo della scheda per garantire l'accessibilità.

- Posizionamento del punto della sonda: Posiziona strategicamente i punti sonda per i test manuali per facilitare un facile accesso da parte dei tecnici.

Implementare strategicamente i punti di test

I punti di test posizionati strategicamente sono essenziali per garantire una copertura completa delle connessioni critiche sul PCB, facilitando test efficienti e diagnosi dei guasti.

Incorporando i punti di test nella progettazione del PCB, gli ingegneri possono garantire che i test unitari siano dettagliati e che i guasti possano essere rapidamente identificati e isolati.

Per ottenere una testabilità ideale, i punti di prova dovrebbero essere posizionati strategicamente tenendo conto dell'accessibilità, dello spazio libero e della distanza requisiti di integrità del segnale. Spaziatura corretta tra i punti di prova è inoltre fondamentale prevenire e garantire cortocircuiti procedure di test affidabili.

Inoltre, i punti di prova posizionati vicino ai componenti chiave consentono un'efficienza isolamento dei guasti e risoluzione dei problemi durante i test.

Il posizionamento efficace dei punti di prova non solo semplifica il processo di prova, ma riduce anche al minimo la complessità delle apparecchiature di prova costi e tempi di prova.

Progettazione verificabile per la producibilità

L'ottimizzazione dei layout PCB per la producibilità richiede un progetto testabile che integri punti ICT su ogni rete di progettazione per garantire una copertura di test approfondita e facilitare flussi di lavoro di produzione efficienti. Questo approccio consente ai produttori a contratto (CM) di condurre test ICT, garantendo che entrambi i lati del PCB siano testati simultaneamente.

Per garantire una testabilità efficace, è necessario seguire le seguenti linee guida:

- Punti di prova accessibili: Garantisce una distanza di 50 mil dai componenti e dalle pastiglie per una facile accessibilità.

- Posizionamento strategico: Posizionare i punti di prova in base alle linee guida DFT per ridurre la complessità delle apparecchiature e potenziali costi aggiuntivi.

- Test manuale semplice: Posizionare i punti della sonda per una facile accessibilità da parte dei tecnici.

- Test coordinati: Collaborare con il CM per coordinare i test ICT per flussi di lavoro di produzione efficienti.

Uso efficiente dei vettori di test

Nel dominio di progettazione per la testabilità, l'uso efficiente dei vettori di test è fondamentale per garantire un test approfondito della funzionalità di un circuito.

Per raggiungere questo obiettivo, è essenziale impiegare metodi efficaci di generazione di vettori in grado di produrre una serie diversificata di vettori di test, ottimizzando così copertura del test.

Metodi di generazione di vettori

Spesso, l'efficienza della progettazione ai fini della testabilità dipende in larga misura dalla generazione effettiva di vettori di test, che sono essenziali per verificare il comportamento di un progetto in prova (DUT).

Nei test unitari, i vettori di test sono modelli di input utilizzati per verificare il comportamento di un DUT e la loro generazione efficiente è fondamentale per una copertura completa della funzionalità del DUT.

Per garantire test efficienti, possono essere impiegati vari algoritmi per la generazione di vettori di test. Questi includono:

- Generazione di vettori di test pseudo-casuali, che bilancia casualità e ripetibilità per test efficaci.

- Generazione esaustiva di vettori di test, che implica la generazione di tutti i possibili modelli di input.

- Generazione intelligente dei vettori, che ottimizza la copertura dei test riducendo al minimo i tempi e le risorse del test.

- Generazione di vettori di test basati su vincoli, che genera vettori di test in base a vincoli specifici e linee guida di testabilità.

Ottimizzazione della copertura del test

Ottimizzazione della copertura del test

La selezione strategica dei punti di test è essenziale per massimizzare la copertura dei guasti nei test PCB, poiché consente l'uso efficiente dei vettori di test per individuare aree specifiche del progetto in prova. Questo approccio garantisce che i potenziali difetti vengano identificati e risolti, riducendo il rischio di PCB difettosi. Una corretta allocazione dei vettori di test può ridurre notevolmente i tempi di test garantendo al tempo stesso una copertura completa.

| Tecniche di ottimizzazione | Benefici |

|---|---|

| Test di scansione dei confini | Efficienza del vettore di test migliorata accedendo ai nodi interni |

| Testare il riutilizzo dei vettori | Riduzione dei tempi di test e migliore allocazione delle risorse |

| Test orientati ai difetti | Test mirati di aree ad alta probabilità di errore |

| Test basati su ATPG | Copertura efficiente dei guasti con generazione automatizzata di modelli di test |

| Test ibridi | Combinazione di diverse tecniche per una copertura completa |

Semplificazione della progettazione di circuiti complessi

La scomposizione di circuiti complessi in componenti più piccoli e più gestibili è un passaggio essenziale per semplificare la progettazione di circuiti complessi. Ciò consente ai progettisti di affrontare ciascun modulo individualmente, migliorando la testabilità complessiva. Questo approccio consente ai progettisti di concentrarsi su moduli specifici, riducendo la complessità del progetto complessivo.

Per raggiungere questo obiettivo, i progettisti possono utilizzare diverse strategie:

- Design modulare: La scomposizione di circuiti complessi in moduli riutilizzabili facilita test e manutenzione.

- Ridurre le dipendenze: Ridurre al minimo le dipendenze tra i componenti semplifica la progettazione e migliora l'isolamento dei guasti.

- Documentazione chiara: Fornire una documentazione concisa e chiara di progetti di circuiti complessi facilita la comprensione e il test della funzionalità del progetto.

- Modelli di progettazione: L'implementazione di modelli di progettazione, come il modello Observer, può semplificare le complesse interazioni dei circuiti e migliorare la testabilità.

Instradamento efficace del segnale per il test

Quando si progetta per la testabilità, efficace instradamento del segnale è fondamentale garantire misurazioni accuratee una strategia di instradamento del segnale ben pianificata può ridurre notevolmente gli errori e migliorarli testare l'efficienza.

Per raggiungere questo obiettivo, è importante ridurre al minimo la lunghezza del segnale per garantire misurazioni accurate. Inoltre, le coppie di segnali differenziali dovrebbero essere instradate insieme per mantenerle integrità del segnale durante i test. Questo impedisce degrado del segnale e garantisce risultati dei test affidabili.

Inoltre, è fondamentale evitare di instradare i segnali vicino a componenti rumorosi per evitare interferenze durante i test. Tracce di impedenza controllata dovrebbe essere utilizzato per mantenere l'integrità e l'accuratezza del segnale durante il test. Ciò garantisce che i segnali di test non siano distorti, fornendo risultati di test affidabili.

Anche l’implementazione di punti di test in posizioni strategiche è fondamentale per un facile accesso e processi di test efficienti. Incorporandoli considerazioni sul design, i progettisti possono assicurarsi che la loro strategia di instradamento del segnale sia ottimizzata per la testabilità, con conseguente test efficiente e accurato.

L'efficace instradamento del segnale è un aspetto critico della progettazione per la testabilità e, seguendo queste migliori pratiche, i progettisti possono garantire test affidabili ed efficienti.

Progettazione per test in-circuit

Quando si progettano schede a circuiti stampati (PCB) per test in-circuit (ICT), è necessario prestare particolare attenzione al posizionamento dei componenti, all'identificazione dei punti di prova, E instradamento del segnale per garantire test efficienti ed efficaci. Ottimizzando questi fattori, i progettisti possono facilitare la copertura ICT e il rapido isolamento dei guasti, riducendo in definitiva i costi di produzione e migliorando la qualità del prodotto.

Nelle sezioni seguenti esamineremo la punti chiave di posizionamento dei componenti accessibili, identificazione dei punti di prova e considerazioni sull'instradamento del segnale che consentono un'ICT di successo.

Posizionamento dei componenti accessibili

Il corretto posizionamento dei componenti accessibili è essenziale nella progettazione dei test in-circuit, poiché consente un posizionamento efficiente dei punti di test e garantisce una copertura completa dei test. Questo è fondamentale per i test unitari, poiché garantisce che il codice di progettazione possa essere testato in modo completo.

Nei test ICT, i punti di test sono posizionati strategicamente per facilitare un facile accesso alle apparecchiature e ai tecnici di test, riducendo la complessità dei test.

Per ottenere il posizionamento ideale dei componenti, i progettisti dovrebbero considerare le seguenti linee guida:

- Requisiti di autorizzazione: Lasciare uno spazio libero di 50 mil dai componenti e di 100 mil dal bordo della scheda.

- Posizionamento del punto di prova: Individua strategicamente i punti di test sul layout del PCB, considerando i requisiti di spazio libero per test efficienti.

- Accessibilità dei componenti: Garantire che i componenti siano accessibili a scopo di test, riducendo la complessità dei test.

- Copertura efficiente del test: Garantire una copertura approfondita del test posizionando i punti di test in modo da consentire test completi.

Identificazione del punto di prova

Alla ricerca di test in-circuit efficienti, identificazione del punto di prova gioca un ruolo fondamentale nella progettazione PCB, poiché consente il posizionamento strategico di punti dedicati sulla scheda per l'ICT. Questo posizionamento deliberato di Punti di prova ICT garantisce che siano facilmente accessibili, con sufficiente distanza dai componenti e dai bordi della scheda, consentendo test efficiente durante la produzione.

Anche la spaziatura adeguata tra i punti di prova è essenziale, poiché garantisce test accurati ed efficienti. Questi punti di test facilitano il collegamento di Apparecchi ICT, consentendo processi di test automatizzati.

Inoltre, i punti di test ben posizionati ed etichettati consentono un rapido test isolamento dei problemi E debug durante l'ICT, facilitando l'identificazione e la correzione dei problemi. L'identificazione efficace dei punti di prova nella progettazione PCB è fondamentale per eseguire test in-circuit efficienti, semplificare il processo di test e ridurre i tempi di produzione.

Considerazioni sull'instradamento del segnale

Le considerazioni sull'instradamento del segnale svolgono un ruolo fondamentale nella progettazione dei test in-circuit, poiché incidono direttamente sull'accuratezza e sull'affidabilità dei risultati dei test. Il corretto instradamento del segnale è essenziale per garantire un test efficiente dei PCB. Nelle TIC, la lunghezza del percorso del segnale dovrebbe essere ridotta al minimo e si dovrebbe utilizzare il routing dell'impedenza controllata per prevenire la degradazione del segnale.

Per ottenere test affidabili, è necessario tenere conto delle seguenti considerazioni sull'instradamento del segnale:

- Ridurre al minimo i crossover: Evitare di incrociare i segnali uno sopra l'altro per evitare interferenze elettromagnetiche e il degrado del segnale.

- Evitare curve strette: Utilizzare percorsi lisci e curvi per evitare riflessioni e radiazioni del segnale.

- Limitare i vias: ridurre al minimo l'uso dei via per prevenire la perdita e il degrado del segnale.

- Posizionamento dei punti di prova strategici: Posizionare i punti di prova in modo strategico per facilitare l'accesso delle sonde di prova, garantendo così test efficienti e affidabili.

Migliorare la copertura e la qualità dei test

Strategie di test efficaci, come incorporando punti ICT su ogni rete progettuale, sono vitali per garantire copertura approfondita del test e qualità nella produzione di PCB. Questo approccio consente test approfonditi, riducendo la probabilità che errori di produzione e guasti dei componenti non vengano rilevati.

Includendo punti di test con una distanza adeguata dai componenti e dal bordo della scheda, i tecnici possono condurre in modo efficiente test unitari e identificare tempestivamente i problemi. Inoltre, l'ICT può essere condotto simultaneamente su entrambi i lati del quadro con il coordinamento del produttore a contratto, semplificando il processo di test.

Inoltre, avere punti sonda facilmente accessibili per i test manuali semplifica le procedure di test, riducendo il rischio di errore umano. Copertura dei test critici e la garanzia della qualità sono essenziali per identificare tempestivamente errori di produzione e guasti dei componenti, garantendo solo questo PCB di alta qualità vengono immessi sul mercato.

Ottimizzazione della progettazione PCB per i test

Quando si ottimizza la progettazione del PCB per i test, è fondamentale tenere in considerazione il posizionamento dei circuiti stampati punti di prova, garantendo che siano facilmente accessibili per test efficienti.

Il corretto posizionamento del punto di prova facilita l'analisi approfondita copertura del test, riduce il tempo di test e aumenta la qualità del test.

Progettare per l'accessibilità

Un layout PCB ben progettato che incorpora punti di test accessibili consente processi di test efficienti, riducendo i tempi e i costi associati all'identificazione e alla correzione dei difetti. La progettazione finalizzata all'accessibilità è un aspetto critico dell'ottimizzazione della progettazione PCB per i test, poiché facilita il processo di test e garantisce una copertura completa dei guasti.

Per ottenere l’accessibilità ideale, i progettisti dovrebbero considerare i seguenti fattori chiave:

- Distanza dai componenti e dai bordi della scheda: Assicurarsi che i punti di test abbiano spazio sufficiente per consentire un facile accesso per testare le sonde.

- Punti ICT su ciascuna rete di progettazione: Incorporare punti ICT su ciascuna rete di progettazione per consentire una copertura di test approfondita durante la produzione.

- Collaborazione con produttori a contratto: Collaborare con i produttori a contratto per determinare le metodologie di test e le modifiche alle apparecchiature più efficaci per una migliore copertura dei guasti.

- Test ICT per un feedback immediato: Utilizza i test ICT per ricevere un feedback immediato sugli errori di produzione, sui guasti dei componenti e sulla funzionalità complessiva del PCB, consentendo regolazioni rapide.

Posizionamento dei punti di prova

Posizionare strategicamente i punti di test su un PCB è essenziale per la massima copertura durante Test TIC, in quanto consente un efficiente rilevamento dei guasti e isolamento durante la produzione. Efficace posizionamento del punto di prova è fondamentale per l'ottimizzazione Progettazione di circuiti stampati per la testabilità. Seguendo Linee guida del DFM, i progettisti possono determinare le posizioni ideali per i punti di test sul PCB, garantendo una copertura ideale e facilitando il rilevamento dei guasti.

Anche una distanza adeguata dai componenti e dai bordi della scheda è fondamentale per facilitare i processi di test. I punti di prova ben posizionati consentono test rapidi e accurati, con conseguente miglioramento della qualità complessiva del prodotto. I requisiti di test ICT dovrebbero essere considerati durante la fase di progettazione per garantire che i punti di test siano posizionati strategicamente per la massima copertura.

Domande frequenti

Quali sono i principi della progettazione per la testabilità?

I principi della progettazione per la testabilità ruotano attorno alla creazione di codice modulare, liberamente accoppiati e facili da testare. Ciò si ottiene aderendo a principi come responsabilità unica, aperto/chiuso, sostituzione di Liskov, segregazione dell'interfaccia e inversione delle dipendenze.

Inoltre, sviluppo guidato dai test, refactoring, E minimizzare le dipendenze sono essenziali per creare codice testabile. Seguendo questi principi, gli sviluppatori possono scrivere codice che sia manutenibile, scalabile e facile da testare, con conseguente miglioramento della qualità del codice e riduzione del debito tecnico.

Cosa sono le tecniche DFT?

Mentre la progettazione PCB tradizionale si concentra sull’estetica e sulla funzionalità, è necessario un cambio di paradigma per dare priorità alla testabilità.

Le tecniche DFT rappresentano un approccio progettuale deliberato che integra considerazioni di test nel layout del PCB. Queste tecniche includono il posizionamento strategico punti di prova, utilizzando tecniche di scansione dei confinie implementazione autotest integrato (BIST) funzionalità.

Quali sono le linee guida PCB nei test?

Le linee guida PCB nei test delineano i requisiti specifici per posizionamento del punto di prova e autorizzazione sui layout dei circuiti stampati. Queste linee guida garantiscono un efficiente isolamento dei guasti e test durante la produzione di PCB, semplificando e migliorando il processo di test rilevamento dei guasti.

Perché è richiesto il DFT?

Il Design for Testability (DFT) è un aspetto essenziale della progettazione PCB. Permette efficiente rilevamento dei guasti e isolamento durante la produzione, riducendo i costi di produzione e il time-to-market. Incorporando i principi DFT, i produttori possono garantire prodotti di alta qualità, ridurre al minimo i difetti e semplificare i processi di test.

L'implementazione efficace del DFT facilita la rapida identificazione e risoluzione dei guasti. Ciò alla fine porta a una migliore affidabilità del prodotto e alla soddisfazione del cliente.