La conception pour la testabilité est un aspect essentiel de la conception des cartes de circuits imprimés (PCB), garantissant des tests efficaces, dès le début. détection de fauteset une réduction du temps et des ressources nécessaires à l'identification des erreurs. Efficace conception pour la testabilité implique la mise en œuvre tester les points de manière stratégique, en maintenant le dégagement et l'accessibilité, et en optimisant routage du signal. Cela comprend également l'utilisation efficace des vecteurs de test, la conception en vue de la fabricabilité et l'amélioration couverture et qualité des tests. En suivant les meilleures pratiques essentielles, les concepteurs peuvent garantir une couverture complète des tests, réduire la complexité des tests et rationaliser la production. À mesure que l’importance de la testabilité continue de croître, la compréhension de ces principes devient de plus en plus importante pour une conception et une fabrication réussies de PCB.

Points clés à retenir

- Garantissez une couverture complète des tests en incorporant des points TIC sur chaque réseau de conception et en plaçant stratégiquement les points de test pour l'accessibilité.

- Mettez en œuvre des stratégies de disposition des circuits imprimés qui maintiennent l'espace libre par rapport aux composants, l'espace libre sur les bords et le placement stratégique des points de sonde afin de réduire la complexité des tests.

- Concevez pour la fabricabilité en plaçant des points TIC sur chaque réseau de conception, en garantissant des points de test accessibles avec un dégagement facile et en suivant les directives DFT.

- Utilisez des vecteurs de test efficaces générés par des méthodes telles que des approches pseudo-aléatoires, exhaustives, intelligentes et basées sur des contraintes pour maximiser la couverture des pannes.

- Améliorez la couverture et la qualité des tests en intégrant des points TIC, en effectuant des tests approfondis et en mettant en œuvre des tests unitaires pour identifier rapidement les erreurs de fabrication et les pannes de composants.

Conception pour les principes fondamentaux de la testabilité

La conception pour la testabilité (DFT) est un concept essentiel dans le développement de logiciels et de matériels qui met l'accent sur la création de des composants qui facilitent les tests, garantissant ainsi une meilleure qualité et fiabilité du produit final.

En intégrant les principes DFT, les développeurs peuvent créer des composants logiciels propices à divers types de tests, y compris les tests unitaires, d'intégration, fonctionnels, de charge et de performances. Cette approche holistique des tests permet au détection de défauts et d'erreurs tôt dans le cycle de développement, réduisant ainsi la probabilité de problèmes en aval.

Un DFT efficace prend en compte l'ensemble du spectre de tests, garantissant que les composants sont conçus dans un souci de testabilité. Cette approche facilite isolation rapide des défauts, réduire le temps et les ressources nécessaire d'identifier et de rectifier erreurs de fabrication et pannes de composants.

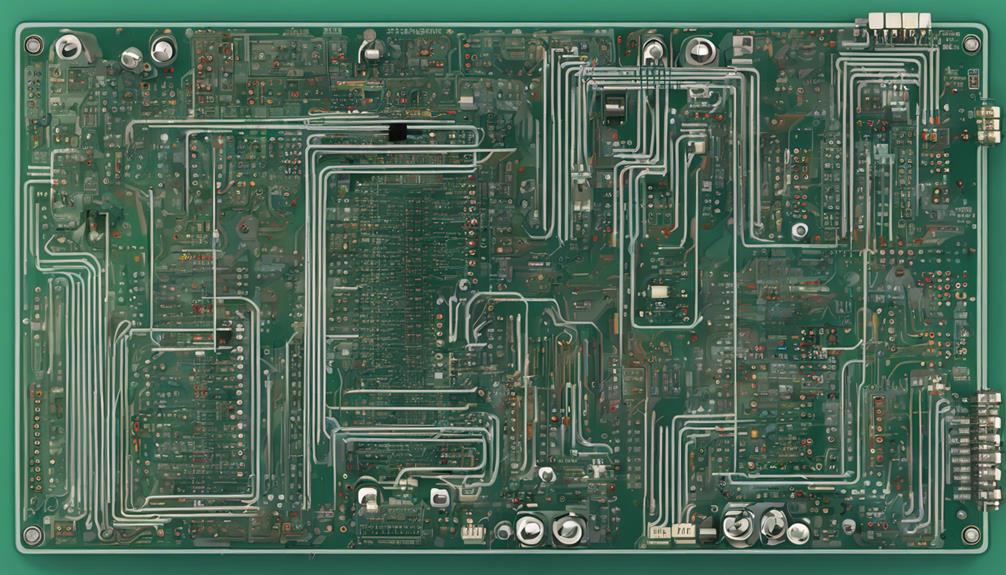

Disposition du PCB pour une testabilité maximale

Pour une testabilité approfondie, les configurations de circuits imprimés (PCB) doivent être conçues avec des points de test intentionnels et des fonctionnalités d'accessibilité qui facilitent des tests efficaces et un diagnostic des défauts. Une configuration PCB bien conçue peut réduire considérablement la complexité et le coût des tests.

Pour obtenir une testabilité maximale, les directives suivantes doivent être suivies :

- Couverture complète des tests: Concevez des configurations de circuits imprimés avec des points TIC sur chaque réseau pour garantir une couverture complète des tests.

- Dégagement des composants: Maintenez un espace minimum de 50 mil entre les points de test, les composants et les plaquettes.

- Dégagement des bords: Maintenez un espace libre de 100 mil entre les points de test et le bord de la planche pour plus d'accessibilité.

- Placement du point de sonde: Placez stratégiquement les points de sonde pour les tests manuels afin de faciliter l'accès des techniciens.

Implémentation stratégique des points de test

Des points de test stratégiquement positionnés sont essentiels pour garantir une couverture complète des connexions critiques sur le PCB, facilitant ainsi tests et diagnostics de pannes efficaces.

En incorporant des points de test dans la conception du PCB, les ingénieurs peuvent s'assurer que les tests unitaires sont détaillés et que les défauts peuvent être rapidement identifiés et isolés.

Pour obtenir une testabilité idéale, les points de test doivent être placés stratégiquement en tenant compte de l'accessibilité, du dégagement et de la sécurité. exigences d'intégrité du signal. Espacement approprié entre les points de test est également essentiel pour éviter les courts-circuits et garantir procédures de test fiables.

De plus, les points de test positionnés à proximité des composants clés permettent une identification des pannes et dépannage pendant les tests.

Le placement efficace des points de test simplifie non seulement le processus de test, mais minimise également la complexité des montages de test, réduisant ainsi coûts et temps de test.

Conception testable pour la fabricabilité

L'optimisation des configurations de circuits imprimés pour la fabricabilité nécessite une conception testable qui intègre des points TIC sur chaque réseau de conception pour garantir une couverture complète des tests et faciliter des flux de production efficaces. Cette approche permet aux fabricants sous contrat (CM) d'effectuer des tests TIC, garantissant que les deux côtés du PCB sont testés simultanément.

Pour garantir une testabilité efficace, les directives suivantes doivent être suivies :

- Points de test accessibles: Garantit un espace libre de 50 mil aux composants et aux plaquettes pour une accessibilité facile.

- Placement stratégique : Positionnez les points de test en fonction des directives DFT pour réduire la complexité des luminaires et les coûts supplémentaires potentiels.

- Tests manuels faciles:Placer les points de sonde pour une accessibilité facile par les techniciens.

- Tests coordonnés: Collaborer avec le CM pour coordonner les tests TIC pour des flux de production efficaces.

Utilisation efficace des vecteurs de test

Dans le domaine de conception pour la testabilité, une utilisation efficace des vecteurs de test est essentielle pour garantir des tests approfondis de la fonctionnalité d'un circuit.

Pour y parvenir, il est essentiel d'employer des méthodes de génération de vecteurs efficaces, capables de produire un ensemble diversifié de vecteurs de test, optimisant ainsi Couverture de test.

Méthodes de génération de vecteurs

Souvent, l’efficacité de la conception pour la testabilité repose en grande partie sur la génération efficace de vecteurs de test, qui sont essentiels pour vérifier le comportement d’une conception testée (DUT).

Dans les tests unitaires, les vecteurs de test sont des modèles d'entrée utilisés pour vérifier le comportement d'un DUT, et leur génération efficace est essentielle pour une couverture complète des fonctionnalités du DUT.

Pour garantir des tests efficaces, divers algorithmes peuvent être utilisés pour la génération de vecteurs de test. Ceux-ci inclus:

- Génération de vecteurs de test pseudo-aléatoires, qui équilibre le caractère aléatoire et la répétabilité pour des tests efficaces.

- Génération exhaustive de vecteurs de test, ce qui implique de générer tous les modèles d'entrée possibles.

- Génération de vecteurs intelligents, qui optimise la couverture des tests tout en minimisant le temps et les ressources des tests.

- Génération de vecteurs de test basée sur des contraintes, qui génère des vecteurs de test basés sur des contraintes spécifiques et des directives de testabilité.

Optimisation de la couverture des tests

Optimisation de la couverture des tests

La sélection stratégique des points de test est essentielle pour maximiser la couverture des défauts dans les tests de PCB, car elle permet l'utilisation efficace des vecteurs de test pour cibler des zones spécifiques de la conception testée. Cette approche garantit que les défauts potentiels sont identifiés et traités, réduisant ainsi le risque de PCB défectueux. Une allocation appropriée des vecteurs de test peut réduire considérablement la durée des tests tout en garantissant une couverture complète.

| Techniques d'optimisation | Avantages |

|---|---|

| Test d'analyse des limites | Efficacité améliorée des vecteurs de test en accédant aux nœuds internes |

| Réutilisation des vecteurs de test | Temps de test réduit et allocation améliorée des ressources |

| Tests orientés sur les défauts | Tests ciblés sur les zones à forte probabilité de panne |

| Tests basés sur l'ATPG | Couverture efficace des défauts avec génération automatisée de modèles de test |

| Tests hybrides | Combiner différentes techniques pour une couverture complète |

Simplifier la conception de circuits complexes

La décomposition de circuits complexes en composants plus petits et plus faciles à gérer est une étape essentielle pour simplifier la conception de circuits complexes. Cela permet aux concepteurs de traiter chaque module individuellement, améliorant ainsi la testabilité globale. Cette approche permet aux concepteurs de se concentrer sur des modules spécifiques, réduisant ainsi la complexité de la conception globale.

Pour y parvenir, les concepteurs peuvent employer plusieurs stratégies :

- Conception modulaire: Décomposer les circuits complexes en modules réutilisables facilite les tests et la maintenance.

- Réduire les dépendances: La minimisation des dépendances entre les composants simplifie la conception et améliore l'isolation des défauts.

- Documentation claire: Fournir une documentation concise et claire sur les conceptions de circuits complexes facilite la compréhension et le test de la fonctionnalité de la conception.

- Modèles de conception: La mise en œuvre de modèles de conception, tels que le modèle Observer, peut simplifier les interactions de circuits complexes et améliorer la testabilité.

Routage efficace du signal pour les tests

Lors de la conception pour la testabilité, efficace routage du signal est essentiel pour garantir mesures précises, et une stratégie de routage des signaux bien planifiée peut réduire considérablement les erreurs et améliorer efficacité des tests.

Pour y parvenir, il est important de minimiser la longueur du signal afin de garantir des mesures précises. De plus, les paires de signaux différentiels doivent être acheminées ensemble pour maintenir l'intégrité du signal pendant les tests. Cela empêche dégradation du signal et assure résultats de tests fiables.

De plus, il est essentiel d’éviter d’acheminer les signaux à proximité de composants bruyants afin d’éviter les interférences pendant les tests. Traces à impédance contrôlée doit être utilisé pour maintenir l’intégrité et la précision du signal pendant les tests. Cela garantit que les signaux de test ne sont pas déformés, fournissant ainsi des résultats de test fiables.

La mise en œuvre de points de test à des emplacements stratégiques est également essentielle pour un accès facile et des processus de test efficaces. En intégrant ces Considérations sur la conception, les concepteurs peuvent s'assurer que leur stratégie de routage des signaux est optimisée pour la testabilité, ce qui se traduit par des tests efficaces et précis.

Le routage efficace des signaux est un aspect essentiel de la conception pour la testabilité, et en suivant ces bonnes pratiques, les concepteurs peuvent garantir des tests fiables et efficaces.

Conception pour les tests en circuit

Lors de la conception de cartes de circuits imprimés (PCB) pour les tests en circuit (TIC), une attention particulière doit être accordée à l'emplacement des composants, à l'identification des points de test, et routage du signal pour garantir des tests efficients et efficaces. En optimisant ces facteurs, les concepteurs peuvent faciliter la couverture des TIC et l'isolation rapide des défauts, réduisant ainsi les coûts de production et améliorant la qualité des produits.

Dans les sections suivantes, nous examinerons les points clés du placement des composants accessibles, de l'identification des points de test et des considérations de routage des signaux qui permettent une TIC réussie.

Placement des composants accessibles

Un placement approprié des composants accessibles est essentiel lors de la conception de tests en circuit, car il permet un placement efficace des points de test et garantit une couverture complète des tests. Ceci est essentiel pour les tests unitaires, car cela garantit que le code de conception peut être testé de manière exhaustive.

Lors des tests TIC, les points de test sont stratégiquement placés pour faciliter l'accès aux équipements de test et aux techniciens, réduisant ainsi la complexité des tests.

Pour obtenir un placement idéal des composants, les concepteurs doivent tenir compte des directives suivantes :

- Exigences de dédouanement: Assurez-vous d'un espace libre de 50 mil par rapport aux composants et d'un espace libre de 100 mil par rapport au bord de la carte.

- Placement des points de test: Localisez stratégiquement les points de test sur la configuration du PCB, en tenant compte des exigences de dégagement pour des tests efficaces.

- Accessibilité des composants: Assurez-vous que les composants sont accessibles à des fins de test, réduisant ainsi la complexité des tests.

- Couverture de test efficace: Garantissez une couverture complète des tests en plaçant les points de test de manière à permettre des tests complets.

Identification des points de test

Dans la poursuite de tests efficaces en circuit, identification du point de test joue un rôle central dans la conception des PCB, car il permet le placement stratégique de points dédiés sur la carte pour les TIC. Ce placement délibéré de Points de test TIC garantit qu'ils sont facilement accessibles, avec un espace suffisant par rapport aux composants et aux bords de la carte, permettant tests efficaces pendant la production.

Un espacement approprié entre les points de test est également essentiel, car il garantit des tests précis et efficaces. Ces points de test facilitent la connexion de Luminaires TIC, permettant des processus de test automatisés.

De plus, des points de test bien placés et étiquetés permettent un isolement d'anomalie et débogage pendant les TIC, facilitant l’identification et la rectification des problèmes. L'identification efficace des points de test dans la conception des PCB est cruciale pour des tests efficaces en circuit, rationalisant le processus de test et réduisant le temps de production.

Considérations sur le routage du signal

Les considérations liées au routage des signaux jouent un rôle essentiel dans la conception des tests en circuit, car elles ont un impact direct sur la précision et la fiabilité des résultats des tests. Un acheminement correct des signaux est essentiel pour garantir des tests efficaces des PCB. Dans les TIC, la longueur du trajet du signal doit être minimisée et un routage à impédance contrôlée doit être utilisé pour éviter la dégradation du signal.

Pour réaliser des tests fiables, les considérations suivantes relatives au routage du signal doivent être prises en compte :

- Minimiser les croisements: Évitez de croiser les signaux les uns sur les autres pour éviter les interférences électromagnétiques et la dégradation du signal.

- Évitez les virages serrés: Utilisez des itinéraires lisses et courbes pour éviter les réflexions et les rayonnements des signaux.

- Limiter les vias: Minimisez l’utilisation de vias pour éviter la perte et la dégradation du signal.

- Placement stratégique des points de test: Placez les points de test de manière stratégique pour faciliter l'accès aux sondes de test, garantissant ainsi des tests efficaces et fiables.

Améliorer la couverture et la qualité des tests

Des stratégies de test efficaces, telles que intégrant des points TIC sur chaque réseau de conception, sont essentiels pour garantir couverture de test approfondie et la qualité dans la fabrication de PCB. Cette approche permet tests approfondis, réduisant ainsi le risque d'erreurs de fabrication et de défaillances de composants non détectées.

En incluant des points de test avec un espacement adéquat par rapport aux composants et au bord de la carte, les techniciens peuvent effectuer efficacement tests unitaires et identifier les problèmes rapidement. De plus, les TIC peuvent être effectuées simultanément des deux côtés de la carte avec la coordination du fabricant sous contrat, rationalisant ainsi le processus de test.

De plus, le fait de disposer de points de sonde facilement accessibles pour les tests manuels simplifie les procédures de test, réduisant ainsi le risque d'erreur humaine. Couverture des tests critiques et l'assurance qualité sont essentielles pour identifier rapidement les erreurs de fabrication et les pannes de composants, garantissant que seuls PCB de haute qualité sont mis sur le marché.

Optimisation de la conception des PCB pour les tests

Lors de l'optimisation de la conception des PCB pour les tests, il est essentiel de prendre en compte l'emplacement des points de test, garantissant qu'ils sont facilement accessibles pour des tests efficaces.

Un placement correct des points de test facilite une Couverture de test, réduit la durée des tests et augmente la qualité des tests.

Conception pour l'accessibilité

Une configuration de circuit imprimé bien conçue qui intègre des points de test accessibles permet des processus de test efficaces, réduisant ainsi le temps et les coûts associés à l'identification et à la correction des défauts. La conception axée sur l'accessibilité est un aspect essentiel de l'optimisation de la conception des circuits imprimés pour les tests, car elle facilite le processus de test et garantit une couverture complète des défauts.

Pour atteindre une accessibilité idéale, les concepteurs doivent prendre en compte les facteurs clés suivants :

- Dégagement des composants et des bords de la carte: Assurez-vous que les points de test disposent d'un espace suffisant pour permettre un accès facile aux sondes de test.

- Points TIC sur chaque réseau de conception: Incorporez des points TIC sur chaque réseau de conception pour permettre une couverture complète des tests pendant la fabrication.

- Collaboration avec des fabricants sous contrat:Travailler avec les fabricants sous contrat pour déterminer les méthodologies de test et les modifications de montage les plus efficaces pour une meilleure couverture des défauts.

- Tests TIC pour un retour immédiat: Utilisez les tests TIC pour recevoir un retour immédiat sur les erreurs de fabrication, les pannes de composants et la fonctionnalité globale des PCB, permettant ainsi des ajustements rapides.

Emplacement des points de test

Placer stratégiquement les points de test sur un PCB est essentiel pour une couverture maximale pendant Tests TIC, car il permet d'être efficace détection de fautes et l'isolement pendant la fabrication. Efficace placement des points de test est essentiel pour optimiser Conception de circuits imprimés pour la testabilité. En suivant Lignes directrices du DFM, les concepteurs peuvent déterminer les emplacements idéaux pour les points de test sur le PCB, garantissant ainsi une couverture idéale et facilitant la détection des défauts.

Un dégagement approprié des composants et des bords des cartes est également essentiel pour faciliter les processus de test. Des points de test bien placés permettent des tests rapides et précis, conduisant à une qualité globale améliorée du produit. Les exigences en matière de tests TIC doivent être prises en compte lors de la phase de conception afin de garantir que les points de test sont stratégiquement placés pour une couverture maximale.

Questions fréquemment posées

Quels sont les principes de conception pour la testabilité ?

Les principes de conception pour la testabilité tournent autour de la création d'un code qui soit modulaire, faiblement couplés et faciles à tester. Ceci est réalisé en adhérant à des principes tels que la responsabilité unique, l'ouverture/fermeture, la substitution Liskov, la ségrégation des interfaces et l'inversion des dépendances.

En plus, développement piloté par les tests, refactorisation, et minimiser les dépendances sont essentiels pour créer du code testable. En suivant ces principes, les développeurs peuvent écrire du code maintenable, évolutif et facile à tester, ce qui améliore la qualité du code et réduit la dette technique.

Que sont les techniques DFT ?

Alors que la conception traditionnelle des PCB se concentre sur l’esthétique et la fonctionnalité, un changement de paradigme est nécessaire pour donner la priorité à la testabilité.

Les techniques DFT sont une approche de conception délibérée qui intègre des considérations de test dans la configuration du PCB. Ces techniques incluent le placement stratégique points de test, en utilisant techniques de balayage des limites, et la mise en œuvre autotest intégré (BIST).

Quelles sont les lignes directrices relatives aux tests concernant les PCB ?

Les directives relatives aux tests de PCB décrivent les exigences spécifiques pour placement des points de test et dégagement sur les configurations de circuits imprimés. Ces directives garantissent une isolation et des tests efficaces des défauts pendant la fabrication des PCB, rationalisant le processus de test et améliorant détection de fautes.

Pourquoi le DFT est-il requis ?

La conception pour la testabilité (DFT) est un aspect essentiel de la conception de PCB. Il permet d'être efficace détection de fautes et l'isolement pendant la fabrication, réduisant ainsi les coûts de production et les délais de mise sur le marché. En intégrant les principes DFT, les fabricants peuvent garantir produits de haute qualité, minimisez les défauts et rationalisez les processus de test.

La mise en œuvre efficace de DFT facilite l’identification et la résolution rapides des défauts. Cela conduit finalement à une amélioration de la fiabilité des produits et de la satisfaction des clients.