Das Design für Testbarkeit ist ein wesentlicher Aspekt des Designs von Leiterplatten (PCB). Es gewährleistet effiziente Tests, frühzeitige Fehlererkennungund reduzierter Zeit- und Ressourcenaufwand für die Fehleridentifizierung. Effektiv Design für Testbarkeit beinhaltet die Umsetzung Testpunkte strategisch, die Einhaltung von Freiräumen und Zugänglichkeit sowie die Optimierung Signalführung. Dazu gehört auch die effiziente Nutzung von Testvektoren, die Entwicklung auf Herstellbarkeit ausgerichteter Designs und die Verbesserung Testabdeckung und -qualität. Durch Befolgen grundlegender Best Practices können Designer eine umfassende Testabdeckung gewährleisten, die Komplexität der Tests verringern und die Produktion optimieren. Da die Bedeutung der Testbarkeit immer weiter zunimmt, wird das Verständnis dieser Prinzipien für ein erfolgreiches PCB-Design und eine erfolgreiche PCB-Herstellung immer wichtiger.

Die zentralen Thesen

- Sorgen Sie für eine umfassende Test-Abdeckung, indem Sie in jedes Designnetz IKT-Punkte integrieren und Testpunkte für die Zugänglichkeit strategisch platzieren.

- Implementieren Sie PCB-Layoutstrategien, die den Abstand zu Komponenten und Kanten sowie die strategische Platzierung von Prüfpunkten wahren, um die Testkomplexität zu reduzieren.

- Achten Sie beim Design auf die Herstellbarkeit, indem Sie in jedem Designnetz ICT-Punkte platzieren, zugängliche Testpunkte mit einfachem Abstand sicherstellen und die DFT-Richtlinien befolgen.

- Verwenden Sie effiziente Testvektoren, die durch Methoden wie pseudozufällige, erschöpfende, intelligente und einschränkungsbasierte Ansätze generiert werden, um die Fehlerabdeckung zu maximieren.

- Verbessern Sie die Testabdeckung und -qualität durch die Einbeziehung von ICT-Punkten, die Durchführung umfassender Tests und die Implementierung von Unit-Tests, um Herstellungsfehler und Komponentenausfälle umgehend zu identifizieren.

Grundlagen des Designs für Testbarkeit

Design for Testability (DFT) ist ein grundlegendes Konzept in der Software- und Hardware-Entwicklung, das die Erstellung von Komponenten, die einfache Tests ermöglichen, wodurch eine bessere Qualität und Zuverlässigkeit des Endprodukts gewährleistet wird.

Durch die Einbeziehung von DFT-Prinzipien können Entwickler Softwarekomponenten erstellen, die dazu beitragen, verschiedene Prüfarten, einschließlich Unit-, Integrations-, Funktions-, Last- und Leistungstests. Dieser ganzheitliche Testansatz ermöglicht die Erkennung von Störungen und Fehlern früh im Entwicklungszyklus, wodurch die Wahrscheinlichkeit späterer Probleme verringert wird.

Effektive DFT berücksichtigt das gesamte Testspektrum und stellt sicher, dass Komponenten unter Berücksichtigung der Testbarkeit entwickelt werden. Dieser Ansatz erleichtert Schnelle Fehlerisolierung, Reduzierung des Zeit- und Ressourcenaufwands erforderlich, um zu identifizieren und zu korrigieren Herstellungsfehler und Bauteilausfälle.

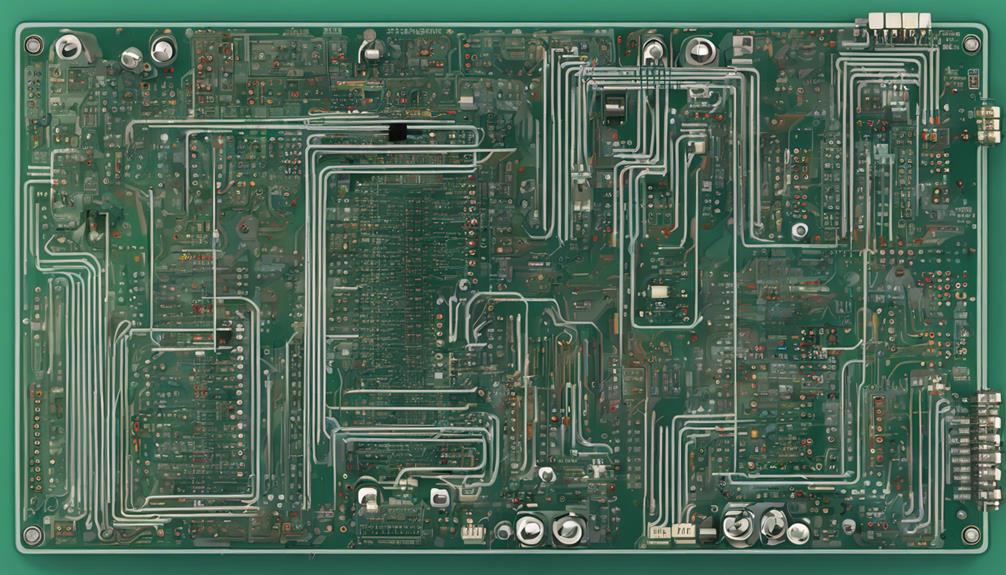

PCB-Layout für maximale Testbarkeit

Für eine gründliche Testbarkeit sollten Leiterplattenlayouts (PCB) mit gezielten Testpunkten und Zugänglichkeitsfunktionen entworfen werden, die effiziente Tests und Fehlerdiagnosen ermöglichen. Ein gut entworfenes PCB-Layout kann die Komplexität und die Kosten von Tests erheblich reduzieren.

Um eine maximale Testbarkeit zu erreichen, sollten die folgenden Richtlinien befolgt werden:

- Gründliche Testabdeckung: Entwerfen Sie PCB-Layouts mit ICT-Punkten auf jedem Netz, um eine umfassende Test-Abdeckung zu gewährleisten.

- Abstand zu Bauteilen: Halten Sie zwischen Testpunkten, Komponenten und Pads einen Mindestabstand von 50 mil ein.

- Randabstand: Halten Sie aus Gründen der Zugänglichkeit einen Abstand von 100 mil zwischen den Testpunkten und der Platinenkante ein.

- Platzierung der Prüfpunkte: Platzieren Sie Prüfpunkte für manuelle Tests strategisch, um den Technikern einen einfachen Zugriff zu ermöglichen.

Testpunkte strategisch implementieren

Strategisch positionierte Testpunkte sind unerlässlich, um eine vollständige Abdeckung kritischer Verbindungen auf der Leiterplatte zu gewährleisten und effiziente Prüfung und Fehlerdiagnose.

Durch die Integration von Testpunkten in das PCB-Design können Ingenieure sicherstellen, dass die Komponententests detailliert sind und Fehler schnell identifiziert und isoliert werden können.

Um eine optimale Testbarkeit zu erreichen, sollten Testpunkte strategisch platziert werden, wobei Zugänglichkeit, Abstand und Anforderungen an die Signalintegrität. Richtiger Abstand zwischen den Testpunkten ist auch wichtig, um Kurzschlüsse zu verhindern und sicherzustellen Zuverlässige Testverfahren.

Darüber hinaus ermöglichen Testpunkte in der Nähe von Schlüsselkomponenten eine effiziente Fehlerisolierung und Fehlerbehebung während des Tests.

Die effektive Platzierung von Testpunkten vereinfacht nicht nur den Testprozess, sondern minimiert auch die Komplexität der Testvorrichtungen und reduziert Prüfkosten und -zeit.

Testbares Design für Herstellbarkeit

Die Optimierung von PCB-Layouts für die Herstellbarkeit erfordert ein testbares Design, das ICT-Punkte in jedes Designnetz integriert, um eine umfassende Testabdeckung zu gewährleisten und effiziente Produktionsabläufe zu ermöglichen. Dieser Ansatz ermöglicht es Auftragsherstellern (CMs), ICT-Tests durchzuführen und sicherzustellen, dass beide Seiten der Leiterplatte gleichzeitig getestet werden.

Um eine effektive Testbarkeit zu gewährleisten, sollten die folgenden Richtlinien beachtet werden:

- Zugängliche Testpunkte: Garantieren Sie einen Abstand von 50 mil zu Komponenten und Pads für einfache Erreichbarkeit.

- Strategische Platzierung: Positionieren Sie Testpunkte basierend auf DFT-Richtlinien, um die Komplexität der Vorrichtung und mögliche Zusatzkosten zu reduzieren.

- Einfaches manuelles Testen: Platzieren Sie Prüfpunkte so, dass sie für Techniker leicht zugänglich sind.

- Koordiniertes Testen: Arbeiten Sie mit dem CM zusammen, um IKT-Tests für effiziente Produktionsabläufe zu koordinieren.

Effiziente Nutzung von Testvektoren

Im Bereich der Design für Testbarkeit, die effiziente Nutzung von Testvektoren ist von entscheidender Bedeutung, um eine gründliche Prüfung der Funktionalität einer Schaltung zu gewährleisten.

Um dies zu erreichen, ist es wichtig, effektive Vektorgenerierungsmethoden einzusetzen, die einen vielfältigen Satz von Testvektoren erzeugen können und so optimieren Testabdeckung.

Methoden zur Vektorgenerierung

Die Effizienz des testgerechten Designs hängt häufig in hohem Maße von der effektiven Generierung von Testvektoren ab, die für die Überprüfung des Verhaltens eines zu testenden Designs (DUT) von entscheidender Bedeutung sind.

Bei Unit-Tests sind Testvektoren Eingabemuster, die zur Überprüfung des Verhaltens eines DUT verwendet werden, und ihre effiziente Generierung ist für eine umfassende Abdeckung der DUT-Funktionalität von entscheidender Bedeutung.

Um effiziente Tests zu gewährleisten, können verschiedene Algorithmen zur Testvektorgenerierung eingesetzt werden. Dazu gehören:

- Pseudozufällige Testvektorgenerierung, das Zufälligkeit und Wiederholbarkeit für effektive Tests ausbalanciert.

- Ausführliche Testvektorgenerierung, bei dem alle möglichen Eingabemuster generiert werden.

- Intelligente Vektorgenerierung, wodurch die Test-Abdeckung optimiert und gleichzeitig Testzeit und -ressourcen minimiert werden.

- Constraint-basierte Testvektorgenerierung, das Testvektoren auf der Grundlage spezifischer Einschränkungen und Testbarkeitsrichtlinien generiert.

Optimieren der Testabdeckung

Optimieren der Testabdeckung

Die strategische Auswahl von Testpunkten ist für die Maximierung der Fehlerabdeckung bei PCB-Tests von entscheidender Bedeutung, da sie die effiziente Verwendung von Testvektoren ermöglicht, um bestimmte Bereiche des zu testenden Designs anzuvisieren. Dieser Ansatz garantiert, dass potenzielle Defekte identifiziert und behoben werden, wodurch das Risiko fehlerhafter PCBs verringert wird. Die richtige Zuweisung von Testvektoren kann die Testzeit erheblich verkürzen und gleichzeitig eine vollständige Abdeckung gewährleisten.

| Optimierungstechniken | Vorteile |

|---|---|

| Boundary-Scan-Tests | Verbesserte Testvektoreffizienz durch Zugriff auf interne Knoten |

| Wiederverwendung von Testvektoren | Reduzierte Testzeit und verbesserte Ressourcenzuweisung |

| Fehlerorientiertes Testen | Gezielte Prüfung von Bereichen mit hoher Fehlerwahrscheinlichkeit |

| ATPG-basiertes Testen | Effiziente Fehlerabdeckung durch automatische Testmustergenerierung |

| Hybridtests | Kombination verschiedener Techniken für eine umfassende Abdeckung |

Vereinfachung des komplexen Schaltungsdesigns

Das Aufteilen komplexer Schaltkreise in kleinere, besser handhabbare Komponenten ist ein wesentlicher Schritt zur Vereinfachung des komplexen Schaltkreisdesigns. Dadurch können Designer jedes Modul einzeln angehen, was die Testbarkeit insgesamt verbessert. Mit diesem Ansatz können sich Designer auf bestimmte Module konzentrieren und so die Komplexität des Gesamtdesigns reduzieren.

Um dies zu erreichen, können Designer mehrere Strategien anwenden:

- Modulares Design: Das Aufteilen komplexer Schaltkreise in wiederverwendbare Module erleichtert das Testen und die Wartung.

- Abhängigkeiten reduzieren: Durch die Minimierung der Abhängigkeiten zwischen Komponenten wird das Design vereinfacht und die Fehlerisolierung verbessert.

- Übersichtliche Dokumentation: Die Bereitstellung einer präzisen und klaren Dokumentation komplexer Schaltungsdesigns erleichtert das Verständnis und Testen der Funktionalität des Designs.

- Designmuster: Die Implementierung von Entwurfsmustern wie dem Observer-Muster kann komplexe Schaltkreisinteraktionen vereinfachen und die Testbarkeit verbessern.

Effektives Signalrouting für Tests

Beim Entwurf auf Testbarkeit, effektive Signalführung ist unerlässlich, um zu gewährleisten genaue Messungenund eine gut geplante Signalführungsstrategie können Fehler erheblich reduzieren und verbessern Testeffizienz.

Um dies zu erreichen, ist es wichtig, die Signallänge zu minimieren, um genaue Messungen zu gewährleisten. Darüber hinaus sollten differenzielle Signalpaare zusammengeführt werden, um Signalintegrität während des Tests. Dies verhindert Signalverschlechterung und sorgt für zuverlässige Testergebnisse.

Darüber hinaus muss unbedingt vermieden werden, Signale in die Nähe von lauten Komponenten zu leiten, um Störungen während des Tests zu verhindern. Kontrollierte Impedanzspuren sollte verwendet werden, um die Signalintegrität und -genauigkeit während des Tests aufrechtzuerhalten. Dadurch wird sichergestellt, dass die Testsignale nicht verzerrt werden und zuverlässige Testergebnisse erzielt werden.

Die Implementierung von Testpunkten an strategischen Standorten ist ebenfalls entscheidend für einen einfachen Zugang und effiziente Testprozesse. Durch die Integration dieser Entwurfsüberlegungenkönnen Designer sicherstellen, dass ihre Signalrouting-Strategie für die Testbarkeit optimiert ist, was zu effizienten und genauen Tests führt.

Eine effektive Signalführung ist ein entscheidender Aspekt des Designs im Hinblick auf die Testbarkeit. Durch Befolgen dieser bewährten Methoden können Designer zuverlässige und effiziente Tests sicherstellen.

Entwerfen für In-Circuit-Tests

Bei der Entwicklung von Leiterplatten für In-Circuit-Tests (ICT) muss die Platzierung der Komponenten, die Identifizierung von Testpunkte, Und Signalführung um effiziente und effektive Tests zu gewährleisten. Durch die Optimierung dieser Faktoren können Designer die IKT-Abdeckung und eine schnelle Fehlerisolierung erleichtern, was letztlich die Produktionskosten senkt und die Produktqualität verbessert.

In den folgenden Abschnitten untersuchen wir die Wichtige Punkte der zugänglichen Komponentenplatzierung, Testpunktidentifizierung und Signalrouting-Überlegungen, die eine erfolgreiche IKT ermöglichen.

Zugängliche Komponentenplatzierung

Die richtige Platzierung zugänglicher Komponenten ist beim Entwurf von In-Circuit-Tests von entscheidender Bedeutung, da sie eine effiziente Platzierung der Testpunkte ermöglicht und eine umfassende Testabdeckung garantiert. Dies ist für Unit-Tests von entscheidender Bedeutung, da dadurch sichergestellt wird, dass der Entwurfscode umfassend getestet werden kann.

Bei IKT-Tests werden Testpunkte strategisch platziert, um den Testgeräten und Technikern einen einfachen Zugang zu ermöglichen und so die Testkomplexität zu reduzieren.

Um eine optimale Komponentenplatzierung zu erreichen, sollten Designer die folgenden Richtlinien beachten:

- Freigabeanforderungen: Stellen Sie sicher, dass ein Abstand von 50 mil zu den Komponenten und ein Abstand von 100 mil zum Rand der Platine eingehalten wird.

- Platzierung der Testpunkte: Platzieren Sie Testpunkte strategisch auf dem PCB-Layout und berücksichtigen Sie dabei die Abstandsanforderungen für effiziente Tests.

- Zugänglichkeit der Komponenten: Stellen Sie sicher, dass Komponenten für Testzwecke zugänglich sind, um die Testkomplexität zu reduzieren.

- Effiziente Testabdeckung: Gewährleisten Sie eine umfassende Testabdeckung, indem Sie die Testpunkte so platzieren, dass umfassende Tests möglich sind.

Testpunktidentifikation

Im Streben nach effizienten In-Circuit-Tests Testpunktidentifikation spielt eine zentrale Rolle im PCB-Design, da es die strategische Platzierung dedizierter Punkte auf der Platine für IKT ermöglicht. Diese gezielte Platzierung von ICT-Testpunkte gewährleistet eine gute Zugänglichkeit mit ausreichend Abstand zu Bauteilen und Platinenrändern, so dass effizientes Testen während der Produktion.

Der richtige Abstand zwischen den Testpunkten ist ebenfalls wichtig, da er genaue und effiziente Tests gewährleistet. Diese Testpunkte erleichtern den Anschluss von IKT-Vorrichtungen, wodurch automatisierte Testprozesse ermöglicht werden.

Darüber hinaus ermöglichen gut platzierte und beschriftete Testpunkte eine schnelle Fehleranalyse Und Fehlersuche während der IKT, wodurch die Identifizierung und Behebung von Problemen erleichtert wird. Eine effektive Testpunktidentifizierung im PCB-Design ist entscheidend für effiziente In-Circuit-Tests, die Rationalisierung des Testprozesses und die Verkürzung der Produktionszeit.

Überlegungen zur Signalführung

Überlegungen zur Signalführung spielen bei der Entwicklung von In-Circuit-Tests eine entscheidende Rolle, da sie sich direkt auf die Genauigkeit und Zuverlässigkeit der Testergebnisse auswirken. Eine ordnungsgemäße Signalführung ist für die Gewährleistung effizienter Tests von Leiterplatten unerlässlich. In der IKT sollten Signalpfadlängen minimiert und eine kontrollierte Impedanzführung genutzt werden, um eine Signalverschlechterung zu verhindern.

Um zuverlässige Tests zu gewährleisten, sollten die folgenden Aspekte der Signalführung berücksichtigt werden:

- Überschneidungen minimieren: Vermeiden Sie die Überschneidung von Signalen, um elektromagnetische Störungen und eine Signalverschlechterung zu verhindern.

- Vermeiden Sie scharfe Kurven: Verwenden Sie glatte, gekrümmte Routen, um Signalreflexionen und -strahlung zu vermeiden.

- Durchkontaktierungen begrenzen: Minimieren Sie die Verwendung von Durchkontaktierungen, um Signalverlust und -verschlechterung zu vermeiden.

- Strategische Testpunktplatzierung: Platzieren Sie Testpunkte strategisch, um den Prüfsonden einen einfachen Zugang zu ermöglichen und so effiziente und zuverlässige Tests sicherzustellen.

Verbesserung der Testabdeckung und -qualität

Effektive Teststrategien wie Einbeziehung von IKT-Punkten auf jedem Designnetz sind entscheidend für die Gewährleistung gründliche Testabdeckung und Qualität in der Leiterplattenherstellung. Dieser Ansatz ermöglicht Umfangreiche Tests, wodurch die Wahrscheinlichkeit verringert wird, dass Herstellungsfehler und Komponentenausfälle unentdeckt bleiben.

Durch die Einbeziehung von Testpunkten mit ausreichendem Abstand zu den Komponenten und zum Rand der Platine können Techniker effizient Komponententests und Probleme umgehend identifizieren. Darüber hinaus kann die ICT in Abstimmung mit dem Vertragshersteller gleichzeitig auf beiden Seiten der Platine durchgeführt werden, was den Testprozess rationalisiert.

Darüber hinaus vereinfachen leicht zugängliche Prüfpunkte für manuelle Tests die Testverfahren und verringern das Risiko menschlicher Fehler. Kritische Testabdeckung und Qualitätssicherung sind unerlässlich, um Fertigungsfehler und Bauteilfehler rechtzeitig zu erkennen und sicherzustellen, dass nur Hochwertige Leiterplatten auf den Markt gebracht.

Optimierung des PCB-Designs für Tests

Bei der Optimierung des PCB-Designs für Tests ist es wichtig, die Platzierung von Testpunkte, und stellen Sie sicher, dass sie für effiziente Tests leicht zugänglich sind.

Die richtige Platzierung der Testpunkte erleichtert die gründliche Testabdeckung, verkürzt die Testzeit und erhöht die Testqualität.

Design für Barrierefreiheit

Ein gut entworfenes PCB-Layout mit zugänglichen Testpunkten ermöglicht effiziente Testprozesse und reduziert den Zeit- und Kostenaufwand bei der Identifizierung und Behebung von Defekten. Ein Design für Zugänglichkeit ist ein entscheidender Aspekt bei der Optimierung des PCB-Designs für Tests, da es den Testprozess erleichtert und eine umfassende Fehlerabdeckung gewährleistet.

Um eine optimale Barrierefreiheit zu erreichen, sollten Designer die folgenden Schlüsselfaktoren berücksichtigen:

- Abstand zu Bauteilen und Platinenrändern: Stellen Sie sicher, dass an den Testpunkten ausreichend Freiraum vorhanden ist, um einen einfachen Zugang für die Testsonden zu ermöglichen.

- IKT-Punkte auf jedem Designnetz: Integrieren Sie ICT-Punkte in jedes Designnetz, um eine umfassende Test-Abdeckung während der Fertigung zu ermöglichen.

- Zusammenarbeit mit Auftragsherstellern: Arbeiten Sie mit Vertragsherstellern zusammen, um die effektivsten Testmethoden und Vorrichtungsmodifikationen für eine verbesserte Fehlerabdeckung zu ermitteln.

- IKT-Tests für sofortiges Feedback: Nutzen Sie IKT-Tests, um sofortiges Feedback zu Herstellungsfehlern, Komponentenausfällen und der allgemeinen PCB-Funktionalität zu erhalten und so schnelle Anpassungen vorzunehmen.

Platzierung der Testpunkte

Die strategische Platzierung von Testpunkten auf einer Leiterplatte ist für eine maximale Abdeckung während IKT-Tests, da es eine effiziente Fehlererkennung und Isolierung während der Herstellung. Effektiv Platzierung der Testpunkte ist entscheidend für die Optimierung PCB-Design für Testbarkeit. Durch Befolgen DFM-Richtlinienkönnen Designer die idealen Positionen für Testpunkte auf der Leiterplatte bestimmen, wodurch eine ideale Abdeckung sichergestellt und die Fehlererkennung erleichtert wird.

Auch der richtige Abstand zu Bauteilen und Platinenrändern ist wichtig, um Testprozesse zu erleichtern. Gut platzierte Testpunkte ermöglichen schnelle und genaue Tests, was zu einer verbesserten Gesamtproduktqualität führt. IKT-Testanforderungen sollten während der Entwurfsphase berücksichtigt werden, um sicherzustellen, dass die Testpunkte strategisch platziert sind, um eine maximale Abdeckung zu gewährleisten.

Häufig gestellte Fragen

Was sind die Designprinzipien für Testbarkeit?

Die Prinzipien des Designs für Testbarkeit drehen sich um die Erstellung von Code, der modular, lose gekoppelt und einfach zu testen. Dies wird durch die Einhaltung von Prinzipien wie Single Responsibility, Open/Closed, Liskov Substitution, Interface Segregation und Dependency Inversion erreicht.

Zusätzlich, testgetriebene Entwicklung, Umstrukturierung, Und Abhängigkeiten minimieren sind für die Erstellung testbaren Codes unerlässlich. Durch Befolgen dieser Prinzipien können Entwickler Code schreiben, der wartbar, skalierbar und einfach zu testen ist, was zu einer verbesserten Codequalität und einer Verringerung der technischen Schulden führt.

Was sind DFT-Techniken?

Während beim traditionellen PCB-Design Ästhetik und Funktionalität im Vordergrund stehen, ist ein Paradigmenwechsel erforderlich, um der Testbarkeit Priorität einzuräumen.

DFT-Techniken sind ein gezielter Designansatz, der Testüberlegungen in das PCB-Layout integriert. Diese Techniken umfassen die strategische Platzierung Testpunkte, mit Boundary-Scan-Technikenund die Umsetzung eingebauter Selbsttest (BIST)-Funktionen.

Was sind PCB-Richtlinien beim Testen?

Die PCB-Testrichtlinien legen spezielle Anforderungen fest für Platzierung der Testpunkte und Freiraum auf Leiterplattenlayouts. Diese Richtlinien garantieren eine effiziente Fehlerisolierung und Prüfung während der Leiterplattenherstellung, rationalisieren den Testprozess und verbessern Fehlererkennung.

Warum ist DFT erforderlich?

Design for Testability (DFT) ist ein wesentlicher Aspekt des PCB-Designs. Es ermöglicht effiziente Fehlererkennung und Isolierung während der Herstellung, wodurch die Produktionskosten und die Markteinführungszeit reduziert werden. Durch die Einbeziehung von DFT-Prinzipien können Hersteller garantieren Produkte mit hoher Qualität, minimieren Sie Defekte und optimieren Sie Testprozesse.

Eine effektive DFT-Implementierung ermöglicht eine schnelle Identifizierung und Behebung von Fehlern. Dies führt letztendlich zu einer verbesserten Produktzuverlässigkeit und Kundenzufriedenheit.