Design pro testovatelnost je základním aspektem návrhu desky s plošnými spoji (PCB), který zajišťuje efektivní testování, včas detekce závadya snížení času a zdrojů pro identifikaci chyb. Efektivní design pro testovatelnost zahrnuje implementaci strategicky testovat bodyudržování volného prostoru a dostupnosti a optimalizace směrování signálu. Zahrnuje také efektivní použití testovacích vektorů, navrhování pro vyrobitelnost a vylepšování pokrytí a kvalitu testu. Dodržováním základních osvědčených postupů mohou návrháři zaručit důkladné pokrytí testováním, snížit složitost testování a zefektivnit výrobu. Jak význam testovatelnosti neustále roste, pochopení těchto principů se stává stále důležitějším pro úspěšný návrh a výrobu desek plošných spojů.

Klíčové věci

- Zajistěte důkladné pokrytí testem začleněním ICT bodů do každé návrhářské sítě a strategickým umístěním testovacích bodů pro dostupnost.

- Implementujte strategie rozmístění desek plošných spojů, které udržují vzdálenost od součástí, vzdálenost od hran a strategické umístění bodů sondy, abyste snížili složitost testování.

- Design pro vyrobitelnost umístěním ICT bodů na každou designovou síť, zajištěním přístupných testovacích bodů se snadným čištěním a dodržováním pokynů DFT.

- Používejte účinné testovací vektory generované metodami, jako jsou pseudonáhodné, vyčerpávající, inteligentní přístupy a přístupy založené na omezeních, abyste maximalizovali pokrytí chyb.

- Zlepšete pokrytí a kvalitu testů začleněním ICT bodů, prováděním rozsáhlého testování a implementací testování jednotek, abyste rychle identifikovali výrobní chyby a selhání součástí.

Design pro základy testovatelnosti

Design for Testability (DFT) je základní koncept ve vývoji softwaru a hardwaru, který klade důraz na tvorbu komponenty, které umožňují snadné testování, čímž je zaručena lepší kvalita a spolehlivost konečného produktu.

Začleněním principů DFT mohou vývojáři vytvářet softwarové komponenty, které k tomu přispívají různé typy testování, včetně testování jednotek, integrace, funkčnosti, zátěže a výkonu. Tento holistický přístup k testování umožňuje odhalování závad a chyb na začátku vývojového cyklu, čímž se snižuje pravděpodobnost následných problémů.

Efektivní DFT bere v úvahu celé spektrum testování a zajišťuje, že komponenty jsou navrženy s ohledem na testovatelnost. Tento přístup usnadňuje rychlá izolace závad, snížení času a zdrojů nutné identifikovat a opravit výrobní chyby a selhání součástí.

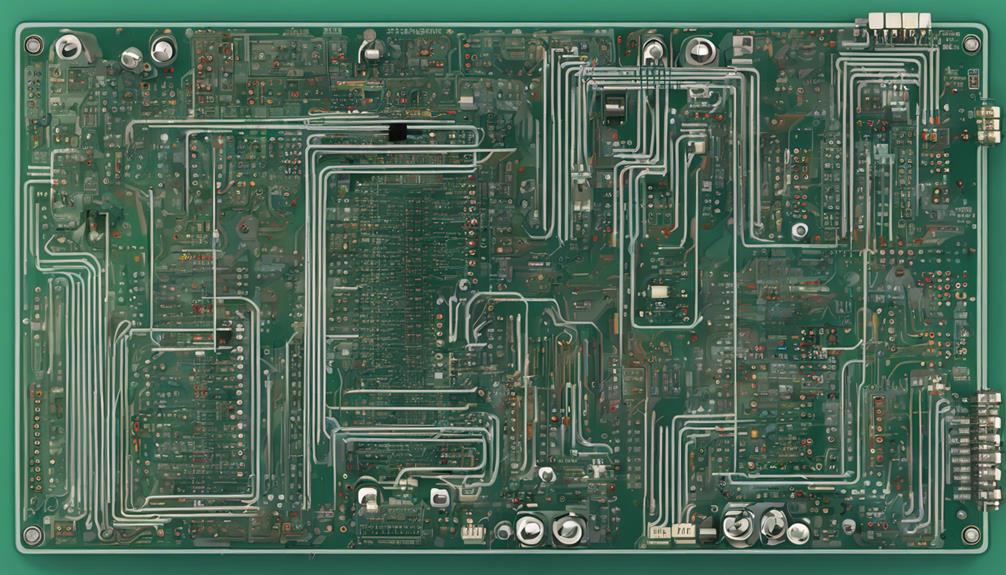

Rozložení PCB pro maximální testovatelnost

Pro důkladnou testovatelnost by měla být rozvržení desek s plošnými spoji (PCB) navrženo se záměrnými testovacími body a funkcemi přístupnosti, které usnadňují účinné testování a diagnostiku chyb. Dobře navržené rozložení PCB může výrazně snížit složitost a náklady na testování.

Pro dosažení maximální testovatelnosti je třeba dodržovat následující pokyny:

- Důkladné pokrytí testem: Navrhněte rozvržení PCB s ICT body na každé síti, abyste zaručili důkladné pokrytí testem.

- Odstup od komponentů: Mezi testovacími body a součástmi a destičkami udržujte minimální vzdálenost 50 mil.

- Vůle okraje: Udržujte vzdálenost 100 mil mezi testovacími body a okrajem desky pro usnadnění přístupu.

- Umístění bodu sondy: Strategicky umístěte body sondy pro ruční testování, abyste měli technikům snadný přístup.

Strategická implementace testovacích bodů

Strategicky umístěné testovací body jsou nezbytné pro zajištění důkladného pokrytí kritických spojení na desce plošných spojů, což usnadňuje efektivní testování a diagnostika závad.

Začleněním testovacích bodů do návrhu desky plošných spojů mohou inženýři zajistit, že testy jednotky jsou podrobné a chyby lze rychle identifikovat a izolovat.

Pro dosažení ideální testovatelnosti by měly být testovací body strategicky umístěny s ohledem na dostupnost, čistotu a požadavky na integritu signálu. Správná vzdálenost mezi testovacími body je také zásadní pro prevenci zkratů a zajištění spolehlivé testovací postupy.

Navíc testovací body umístěné v blízkosti klíčových komponent umožňují efektivní izolování závad a odstraňování závad během testování.

Efektivní umístění testovacích bodů nejen zjednodušuje proces testování, ale také minimalizuje složitost testovacích přípravků a snižuje náklady na testování a čas.

Testovatelný design pro vyrobitelnost

Optimalizace rozvržení desek plošných spojů z hlediska vyrobitelnosti vyžaduje testovatelný návrh, který integruje ICT body do každé návrhové sítě, aby bylo zaručeno důkladné pokrytí testem a usnadněny efektivní výrobní pracovní postupy. Tento přístup umožňuje smluvním výrobcům (CM) provádět testování ICT a zajistit, že obě strany PCB budou testovány současně.

Aby byla zaručena efektivní testovatelnost, je třeba dodržovat následující pokyny:

- Přístupné testovací body: Zaručte vzdálenost 50 mil od komponentů a destiček pro snadný přístup.

- Strategické umístění: Umístěte testovací body na základě pokynů DFT, abyste snížili složitost příslušenství a potenciální dodatečné náklady.

- Snadné ruční testování: Umístěte body sondy tak, aby byly pro techniky snadno dostupné.

- Koordinované testování: Spolupracujte s CM na koordinaci testování ICT pro efektivní produkční pracovní postupy.

Efektivní využití testovacích vektorů

V doméně design pro testovatelnostÚčinné využití testovacích vektorů je zásadní pro zaručení důkladného testování funkčnosti obvodu.

Abychom toho dosáhli, je nezbytné použít účinné metody generování vektorů, které mohou produkovat různorodou sadu testovacích vektorů, a tím optimalizovat testovací pokrytí.

Metody generování vektorů

Účinnost návrhu pro testovatelnost často silně závisí na efektivním generování testovacích vektorů, které jsou zásadní pro ověření chování testovaného návrhu (DUT).

Při testování jednotek jsou testovací vektory vstupními vzory používanými k ověření chování zkoušeného zařízení a jejich efektivní generování je rozhodující pro důkladné pokrytí funkčnosti zkoušeného zařízení.

Aby bylo zaručeno efektivní testování, mohou být pro generování testovacích vektorů použity různé algoritmy. Tyto zahrnují:

- Generování pseudonáhodného testovacího vektoru, který vyvažuje náhodnost a opakovatelnost pro efektivní testování.

- Generování vyčerpávajícího testovacího vektoru, což zahrnuje generování všech možných vstupních vzorů.

- Inteligentní generování vektorů, která optimalizuje testovací pokrytí a zároveň minimalizuje dobu testování a zdroje.

- Generování testovacích vektorů na základě omezení, který generuje testovací vektory na základě specifických omezení a pokynů pro testovatelnost.

Optimalizace testovacího pokrytí

Optimalizace testovacího pokrytí

Strategický výběr testovacích bodů je nezbytný pro maximalizaci pokrytí chyb při testování PCB, protože umožňuje efektivní využití testovacích vektorů pro cílení na konkrétní oblasti testovaného návrhu. Tento přístup zaručuje identifikaci a řešení potenciálních defektů, čímž se snižuje riziko chybných PCB. Správná alokace testovacích vektorů může výrazně zkrátit dobu testování a zároveň zajistit důkladné pokrytí.

| Optimalizační techniky | Výhody |

|---|---|

| Testování Boundary Scan | Vylepšená efektivita testovacího vektoru díky přístupu k interním uzlům |

| Znovu použít testovací vektor | Zkrácená doba testování a lepší alokace zdrojů |

| Testování zaměřené na vady | Cílené testování oblastí s vysokou pravděpodobností poruch |

| Testování založené na ATPG | Efektivní pokrytí chyb s automatickým generováním testovacích vzorů |

| Hybridní testování | Kombinace různých technik pro komplexní pokrytí |

Zjednodušení komplexního návrhu obvodů

Rozdělení složitých obvodů na menší, lépe ovladatelné komponenty je nezbytným krokem ke zjednodušení komplexního návrhu obvodů. To umožňuje návrhářům řešit každý modul individuálně, čímž se zvyšuje celková testovatelnost. Tento přístup umožňuje návrhářům zaměřit se na konkrétní moduly, čímž se snižuje složitost celkového návrhu.

K dosažení tohoto cíle mohou návrháři použít několik strategií:

- Modulární design: Rozdělení složitých obvodů na opakovaně použitelné moduly usnadňuje testování a údržbu.

- Snížit závislosti: Minimalizace závislostí mezi komponentami zjednodušuje návrh a zlepšuje izolaci chyb.

- Přehledná dokumentace: Poskytování stručné a jasné dokumentace komplexních návrhů obvodů usnadňuje pochopení a testování funkčnosti návrhu.

- Designové vzory: Implementace návrhových vzorů, jako je vzor Observer, může zjednodušit složité interakce obvodů a zlepšit testovatelnost.

Efektivní směrování signálu pro test

Při navrhování pro testovatelnost, efektivní směrování signálu je nezbytné zaručit přesná měřenía dobře naplánovaná strategie směrování signálu může výrazně snížit chyby a zlepšit účinnost testování.

K dosažení tohoto cíle je důležité minimalizovat délku signálu, aby byla zajištěna přesná měření. Kromě toho by páry diferenciálních signálů měly být směrovány společně, aby se zachovaly integrita signálu během testování. To zabraňuje degradace signálu a zajišťuje spolehlivé výsledky testů.

Kromě toho je důležité vyhnout se směrování signálů v blízkosti hlučných komponent, aby se zabránilo rušení během testování. Řízené impedanční stopy by měly být použity k udržení integrity a přesnosti signálu během testování. Tím je zajištěno, že testovací signály nejsou zkresleny, což poskytuje spolehlivé výsledky testu.

Implementace testovacích bodů na strategických místech je také zásadní pro snadný přístup a efektivní testovací procesy. Začleněním těchto designové úvahy, návrháři se mohou ujistit, že jejich strategie směrování signálu je optimalizována pro testovatelnost, což vede k efektivnímu a přesnému testování.

Efektivní směrování signálu je kritickým aspektem návrhu pro testovatelnost a dodržením těchto osvědčených postupů mohou návrháři zajistit spolehlivé a efektivní testování.

Navrhování pro testování v obvodu

Při navrhování desek plošných spojů (PCB) pro in-circuit testing (ICT) je třeba pečlivě zvážit umístění součástek, identifikaci testovací body, a směrování signálu aby bylo zaručeno účinné a efektivní testování. Optimalizací těchto faktorů mohou konstruktéři usnadnit pokrytí ICT a rychlou izolaci chyb, v konečném důsledku snížit výrobní náklady a zlepšit kvalitu produktu.

V následujících částech prozkoumáme Klíčové body přístupné umístění komponent, identifikace testovacích bodů a úvahy o směrování signálu, které umožňují úspěšné ICT.

Přístupné umístění komponent

Správně přístupné umístění součástí je zásadní při navrhování pro testování v okruhu, protože umožňuje efektivní umístění testovacích bodů a zaručuje důkladné pokrytí testem. To je zásadní pro testování jednotek, protože zajišťuje, že návrhový kód lze testovat komplexně.

Při testování ICT jsou testovací body strategicky umístěny tak, aby usnadňovaly snadný přístup pro testovací zařízení a techniky, což snižuje složitost testování.

Pro dosažení ideálního umístění komponent by měli návrháři zvážit následující pokyny:

- Požadavky na povolení: Zajistěte vzdálenost 50 mil od součástí a 100 mil od okraje desky.

- Umístění zkušebního bodu: Strategicky umístěte testovací body na plošném spoji s ohledem na požadavky na vůli pro účinné testování.

- Přístupnost komponent: Zajistěte, aby komponenty byly přístupné pro účely testování, čímž se sníží složitost testování.

- Efektivní pokrytí testem: Zaručte důkladné pokrytí testem umístěním testovacích bodů způsobem, který umožňuje komplexní testování.

Identifikace testovacího bodu

Ve snaze o účinné testování v okruhu, identifikace testovacího bodu hraje klíčovou roli v návrhu PCB, protože umožňuje strategické umístění vyhrazených bodů na desce pro ICT. Toto záměrné umístění Testovací body ICT zajišťuje, že jsou snadno přístupné, s dostatečnou vzdáleností od součástí a okrajů desky, což umožňuje efektivní testování při výrobě.

Správná vzdálenost mezi testovacími body je také nezbytná, protože zajišťuje přesné a efektivní testování. Tyto testovací body usnadňují připojení ICT přípravky, umožňující automatizované testovací procesy.

Dobře umístěné a označené testovací body navíc umožňují rychlé izolace poruch a ladění během ICT, což usnadňuje identifikaci a nápravu problémů. Efektivní identifikace testovacích bodů v návrhu PCB je zásadní pro efektivní testování v obvodu, zefektivnění testovacího procesu a zkrácení doby výroby.

Úvahy o směrování signálu

Úvahy o směrování signálu hrají zásadní roli při navrhování pro testování v obvodu, protože přímo ovlivňují přesnost a spolehlivost výsledků testů. Správné směrování signálu je nezbytné pro zajištění účinného testování desek plošných spojů. V ICT by délky signálových cest měly být minimalizovány a mělo by být použito směrování s řízenou impedancí, aby se zabránilo degradaci signálu.

Pro dosažení spolehlivého testování je třeba vzít v úvahu následující aspekty směrování signálu:

- Minimalizujte výhybky: Vyhněte se křížení signálů přes sebe, abyste zabránili elektromagnetickému rušení a degradaci signálu.

- Vyhněte se ostrým ohybům: Použijte hladké, zakřivené trasy, abyste zabránili odrazům signálu a záření.

- Omezit průchody: Minimalizujte použití prokovů, abyste zabránili ztrátě a degradaci signálu.

- Strategické umístění testovacích bodů: Umístěte testovací body strategicky, abyste usnadnili snadný přístup k testovacím sondám a zajistili tak efektivní a spolehlivé testování.

Zlepšení pokrytí a kvality testů

Efektivní testovací strategie, jako např začlenění ICT bodů na každé designové síti jsou zásadní pro zaručení důkladné testovací pokrytí a kvalitu výroby DPS. Tento přístup umožňuje rozsáhlé testování, což snižuje pravděpodobnost, že výrobní chyby a selhání součástí zůstanou neodhaleny.

Zahrnutím testovacích bodů s dostatečnou vzdáleností od součástí a okraje desky mohou technici efektivně provádět testování jednotky a rychle identifikovat problémy. Kromě toho lze ICT provádět současně na obou stranách desky s koordinací od smluvního výrobce, což zjednodušuje testovací proces.

Snadno přístupné body sondy pro ruční testování navíc zjednodušují testovací postupy a snižují riziko lidské chyby. Pokrytí kritických testů a zajištění kvality jsou zásadní pro rychlou identifikaci výrobních chyb a selhání součástí a zajišťují pouze to vysoce kvalitní desky plošných spojů jsou uvedeny na trh.

Optimalizace návrhu PCB pro test

Při optimalizaci návrhu desky plošných spojů pro testování je důležité vzít v úvahu umístění testovací body, zajišťující, že jsou snadno dostupné pro efektivní testování.

Správné umístění testovacích bodů usnadňuje důkladné testovací pokrytí, zkracuje dobu testování a zvyšuje kvalitu testu.

Design pro usnadnění

Dobře navržené rozložení desek plošných spojů, které zahrnuje přístupné testovací body, umožňuje efektivní testovací procesy, snižuje čas a náklady spojené s identifikací a opravou závad. Design pro přístupnost je kritickým aspektem optimalizace návrhu PCB pro testování, protože usnadňuje proces testování a zajišťuje důkladné pokrytí chyb.

Pro dosažení ideální dostupnosti by měli návrháři zvážit následující klíčové faktory:

- Vzdálenost od součástek a hran desky: Ujistěte se, že testovací body mají dostatečný volný prostor, aby byl umožněn snadný přístup pro testovací sondy.

- ICT body na každé designové síti: Zahrňte ICT body do každé konstrukční sítě, abyste umožnili důkladné testování během výroby.

- Spolupráce se smluvními výrobci: Spolupracujte se smluvními výrobci na určení nejúčinnějších testovacích metodologií a úprav přípravků pro lepší pokrytí chyb.

- Testování ICT pro okamžitou zpětnou vazbu: Využijte testování ICT k získání okamžité zpětné vazby o výrobních chybách, poruchách součástí a celkové funkčnosti desek plošných spojů, což umožňuje rychlé úpravy.

Umístění testovacího bodu

Strategické umístění testovacích bodů na PCB je nezbytné pro maximální pokrytí během testování ICT, protože umožňuje efektivní detekce závady a izolace během výroby. Efektivní umístění zkušebního bodu je rozhodující pro optimalizaci Návrh PCB pro testovatelnost. Sledováním pokyny DFM, mohou návrháři určit ideální umístění pro testovací body na desce plošných spojů, což zajistí ideální pokrytí a usnadní detekci chyb.

Pro usnadnění testovacích procesů je také životně důležitá správná vzdálenost od součástí a okrajů desky. Dobře umístěné testovací body umožňují rychlé a přesné testování, což vede ke zlepšení celkové kvality produktu. Požadavky na testování ICT by měly být zváženy ve fázi návrhu, aby bylo zajištěno, že testovací body jsou strategicky umístěny pro maximální pokrytí.

Často kladené otázky

Jaké jsou principy návrhu pro testovatelnost?

Principy návrhu pro testovatelnost se točí kolem vytváření kódu, který je modulární, volně spojené a snadno testovatelné. Toho je dosaženo dodržováním principů, jako je Single Responsibility, Open/Closed, Liskov Substitution, Interface Segregation a Dependency Inversion.

Dodatečně, testem řízený vývoj, refaktorování, a minimalizace závislostí jsou nezbytné pro tvorbu testovatelného kódu. Dodržováním těchto zásad mohou vývojáři psát kód, který je udržovatelný, škálovatelný a snadno testovatelný, což vede ke zlepšení kvality kódu a snížení technického dluhu.

Co jsou techniky DFT?

Zatímco tradiční design PCB se zaměřuje na estetiku a funkčnost, je nutná změna paradigmatu, aby byla upřednostněna testovatelnost.

Techniky DFT jsou záměrným návrhovým přístupem, který integruje úvahy o testování do rozvržení PCB. Tyto techniky zahrnují strategické umístění testovací body, použitím techniky hraničního skenovánía provádění vestavěný autotest (BIST) schopnosti.

Jaké jsou pokyny pro PCB při testování?

Pokyny pro PCB při testování nastiňují specifické požadavky na umístění zkušebního bodu a vůle na rozvržení desek plošných spojů. Tyto pokyny zaručují účinnou izolaci chyb a testování během výroby desek plošných spojů, zefektivňují proces testování a zlepšují detekce závady.

Proč je vyžadováno DFT?

Design for Testability (DFT) je základním aspektem návrhu PCB. Umožňuje efektivní detekce závady a izolace během výroby, což snižuje výrobní náklady a dobu uvedení na trh. Začleněním principů DFT mohou výrobci zaručit vysoce kvalitní produktyminimalizovat vady a zefektivnit testovací procesy.

Efektivní implementace DFT usnadňuje rychlou identifikaci a řešení poruch. To v konečném důsledku vede ke zvýšení spolehlivosti produktů a spokojenosti zákazníků.